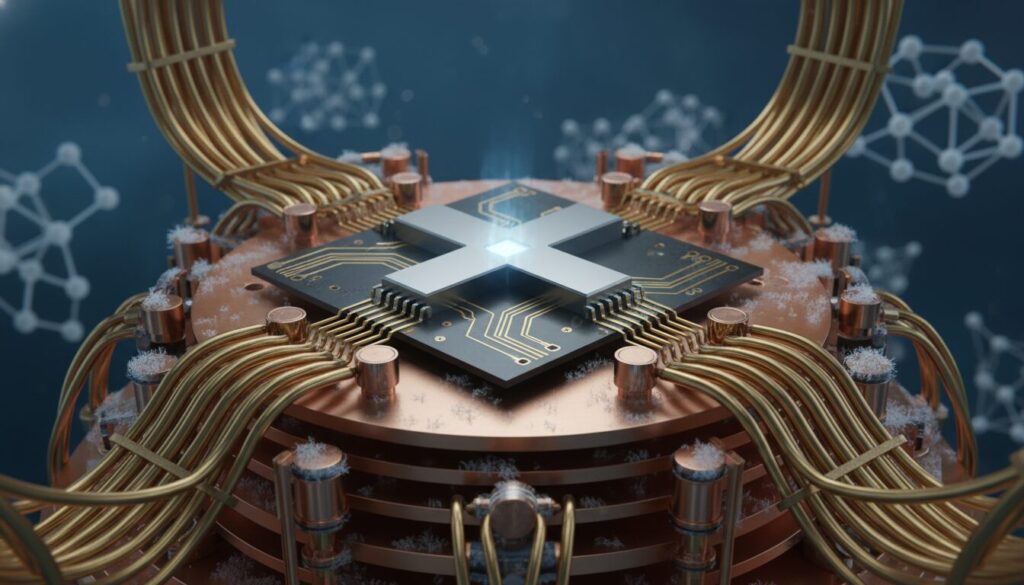

現代のディープテック領域において、最も激しい覇権争いが繰り広げられているのが量子コンピュータのハードウェア開発である。その中で、GoogleやIBMといった巨大テック企業のみならず、近年の日本における国産量子コンピュータ初号機でも採用され、業界のメインストリームとして確固たる地位を築いているのが「超伝導方式(超伝導量子ビット)」だ。

しかし、一般メディアで語られる「夢の超高速計算機」というバラ色のシナリオの裏側には、量子力学特有の脆弱性、極低温環境における熱力学的限界、そして微細加工に伴うクロストークや相関エラーといった、極めてシビアなエンジニアリング上の壁が立ちはだかっている。表面的なスペック比較や単なる期待値だけで技術選定を行うことは、企業R&Dやディープテック投資において致命的なリスクとなり得る。

本稿では、テクノロジー専門メディア「TechShift」の視点から、超伝導量子ビットの基礎原理、他方式(イオントラップ、光、冷却原子など)との徹底的な比較、日本国内の独自エコシステムの現在地、そして2030年代の実用化(FTQC:誤り耐性量子計算)に向けた技術的課題と未来のロードマップまでを、圧倒的な情報量とフラットな技術的視点から完全に解き明かす。

- 超伝導量子ビットとは? 仕組みと他方式に対する圧倒的優位性

- 基礎原理:ジョセフソン接合と超伝導回路が作る人工原子

- 超伝導特有の物理的落とし穴:二準位系(TLS)とデコヒーレンス

- イオントラップ・光・冷却原子方式との徹底比較と限界

- 日本が世界を牽引する「国産量子コンピュータ」の現在地

- 理研・JSTの快挙:64量子ビット初号機「叡」のアーキテクチャ解析

- 通信技術との融合:NTTの高精度制御とNICTの分散型ネットワーク

- 産学連携の課題と次世代サプライチェーンの構築

- 実用化への最大の壁:技術的課題(エラー・スケーラビリティ)の最前線

- 量子ビット寿命と高精度操作のトレードオフをどう突破するか

- 量子エラー訂正(QEC)と表面符号実装の「オーバーヘッド問題」

- 冷却インフラと配線の限界を突破する:極低温CMOSと3D実装技術

- 投資家・CTO必見:超伝導量子技術の産業インパクトと未来ロードマップ

- 2026〜2030年の予測シナリオ:NISQ後期からアーリーFTQCへの移行

- 企業R&Dが備えるべき技術戦略とユースケースの開拓

- ディープテック投資から見る次世代周辺技術の勝機と市場予測

超伝導量子ビットとは? 仕組みと他方式に対する圧倒的優位性

企業のR&D部門や技術戦略担当者が技術選定を行う上で不可欠となるのは、各方式の根底にある物理法則の違いを正確に把握することである。本セクションでは、超伝導方式がなぜ現在ハードウェア開発のメインストリームを走っているのか、その基礎原理から、物理的限界、そして競合する他方式との客観的かつ定量的な比較までを解説する。

基礎原理:ジョセフソン接合と超伝導回路が作る人工原子

超伝導量子ビットの核心は、巨視的な電気回路を用いて量子力学的な振る舞いを人工的に作り出し、高度な量子情報処理を実現する点にある。一般的に、通常のLC共振回路(コイルとコンデンサで構成される回路)でもエネルギー状態は量子化されるが、そのエネルギー準位が等間隔(調和振動子)になるため、特定の2準位(例えば基底状態の0と、第一励起状態の1)だけを選択的に操作することができない。

これを解決するための魔法の素子が、非線形インダクタンス素子である「ジョセフソン接合(Josephson Junction)」だ。ジョセフソン接合は、2つの超伝導体(アルミニウムやニオブなど)の間に、数ナノメートルという極薄の絶縁体層(酸化アルミニウムなど)を挟み込んだ構造を持つ。極低温下において、超伝導を担う電子対(クーパー対)がこの絶縁層を量子トンネル効果によって通り抜ける際、非線形なインダクタンスが発生する。

この接合を超伝導回路に組み込むことで、エネルギー準位の間隔に非線形性(非調和性)が生まれ、最下底の2つの状態のみを独立した「人工原子」としてマイクロ波パルスで操作することが可能になる。現在主流となっている「トランズモン(Transmon)型」の超伝導量子ビットは、このジョセフソン接合に並列に大きなキャパシタを接続することで、電荷の揺らぎ(チャージノイズ)に対する耐性を劇的に高めたアーキテクチャである。最大の強みは、既存のCMOS半導体製造プロセス(リソグラフィ技術)を応用してシリコンまたはサファイアウェハー上に回路を微細加工できる点にある。この「設計の自由度」と「半導体産業の巨大なインフラ転用」こそが、莫大な資本が継続投下される根本的理由である。

超伝導特有の物理的落とし穴:二準位系(TLS)とデコヒーレンス

圧倒的なスケーラビリティのポテンシャルを持つ一方で、超伝導量子ビットは巨視的な回路であるため、環境ノイズに対して極めて脆弱である。特に、エンジニアリング上の最大の敵とされているのが「二準位系(TLS: Two-Level System)欠陥」と呼ばれるミクロな不純物や構造欠陥だ。

TLSは、金属表面の酸化膜、基板との境界面、あるいはレジスト残渣などに無数に存在し、量子ビットが持つエネルギーを意図せず吸収してしまう。これにより、量子状態が古典的な状態へと崩壊する「デコヒーレンス(エネルギー緩和および位相緩和)」が引き起こされる。さらに近年、極低温環境下であっても、微小な熱励起や放射線(後述)によって「準粒子(Quasiparticle:対を成していない単独の電子)」が生成され、これがジョセフソン接合を横切ることで致命的なエラーを引き起こす現象も深刻な問題として顕在化している。超伝導方式の開発は、いかにしてこの材料表面の微視的な物理現象を制御し、ノイズを隔離するかという果てしない材料科学の戦いでもある。

イオントラップ・光・冷却原子方式との徹底比較と限界

次世代の技術選定において、超伝導方式はどのような立ち位置にあるのか。近年急速に台頭している「冷却原子(中性原子)方式」も含め、客観的なデータに基づく比較を行う。

| 比較項目 | 超伝導方式(Superconducting) | イオントラップ方式(Ion Trap) | 光方式(Photonic) | 冷却原子方式(Neutral Atom) |

|---|---|---|---|---|

| 動作速度(ゲート時間) | 10〜100ナノ秒(極めて高速) | 10〜100マイクロ秒(低速) | ピコ秒〜ナノ秒(最速クラス) | 数百ナノ〜数マイクロ秒(中速) |

| 量子ビット寿命(コヒーレンス時間) | 100マイクロ秒〜数ミリ秒(短〜中程度) | 数秒〜数十分(極めて長い) | 光子消失が課題(物理概念が異なる) | 数秒以上(長い) |

| スケーラビリティ・集積性 | 半導体プロセスによる高集積化が容易だが、配線制約あり | 真空チャンバーと電極配線の肥大化が課題 | 光回路の小型化と極低温光子検出器が課題 | 光ピンセットによる2次元/3次元の動的配列に強み |

| 動作環境 | 絶対零度付近(約15mK)の希釈冷凍機が必須 | 超高真空環境(室温動作の可能性あり) | 室温動作が可能(一部検出器のみ極低温) | 超高真空環境・レーザー冷却システム |

超伝導方式の圧倒的優位性は、その「動作速度の速さ」にある。イオントラップ方式や冷却原子方式は、自然界の原子そのものを利用するためすべてのビットが完全に均質であり、コヒーレンス時間が圧倒的に長いという長所を持つ。しかし、ゲート操作に要する時間が超伝導の100倍〜1,000倍かかるため、複雑なアルゴリズムを実行する際の総計算時間において大きなボトルネックが生じる。

一方で、超伝導方式の限界も明確である。絶対零度に近い約15mK(ミリケルビン)という極低温環境を維持するための巨大な希釈冷凍機が必須であり、ビット数が増えるほどチップへ繋がる極低温同軸ケーブルからの熱流入が物理的限界を迎える(配線問題)。近年急成長している冷却原子方式が、室温環境の真空チャンバー内で数千個の原子を光ピンセットで高密度配列できるアーキテクチャを提示していることは、超伝導方式に対する強力なパラダイムシフトの脅威となっている。超伝導陣営は、この巨大なインフラコストと配線問題を解決しなければ、アーリーFTQC(初期の誤り耐性量子計算)のフェーズで他方式に追い抜かれるリスクを孕んでいる。

日本が世界を牽引する「国産量子コンピュータ」の現在地

超伝導方式は、その製造に高度な半導体微細加工プロセスと材料工学を要求する。実は、その中核をなす超伝導回路とジョセフソン接合の精密な設計・製造技術、さらには周辺のマイクロ波制御機器において、日本が世界トップクラスの技術資産を有していることは、テクノロジー市場における極めて重要なファクトである。本セクションでは、国内の主要プレイヤーがいかにして国産量子コンピュータのエコシステムを構築しているのか、その最前線とロードマップを一次情報に基づいて紐解く。

理研・JSTの快挙:64量子ビット初号機「叡」のアーキテクチャ解析

2023年、日本のディープテック業界に最大の衝撃を与えたのが、理化学研究所(理研)と科学技術振興機構(JST)、富士通などを中心とした共同研究グループによる、64量子ビットの超伝導量子コンピュータ初号機「叡(えい)」の稼働とクラウドサービスの公開である。これは単なる実験室レベルの「PoC(概念実証)」ではなく、本格的な社会実装を見据えた歴史的マイルストーンだ。

技術的に注目すべきは、「叡」のアーキテクチャが、将来的な量子エラー訂正の実装に不可欠となる「表面符号(Surface Code)」の実行を前提とした2次元平面配列を採用している点である。64個の量子ビットと可変結合器(Tunable Coupler)が規則正しく正方格子状に配置され、隣接ビット間での高精度な2量子ビットゲート操作(エンタングルメントの生成)を実現している。さらに、パッケージングにおいては、信号線や制御線を3次元的に配線する「フリップチップ実装技術」を取り入れ始めており、チップ平面の面積制約を突破するロードマップが明確に敷かれている。

この計算リソースがクラウド経由で国内企業や研究機関に提供されたことで、創薬シミュレーション、新材料探索、金融モデリングなど、量子情報処理を活用した実機ベースのユースケース開発が一気に加速した。理研を中心とするコンソーシアムは、2025年ごろに100量子ビット級、2030年代初頭には1,000量子ビット級へとスケールアウトさせる明確な開発計画を推進している。

通信技術との融合:NTTの高精度制御とNICTの分散型ネットワーク

量子チップ自体の開発に並び、日本の競争力を決定づけているのが「周辺インフラと制御技術」の圧倒的な厚みである。超伝導量子ビットの性能を極限まで引き出すためには、数ナノ秒単位での正確なマイクロ波パルスの照射と、極微弱な信号の読み出し制御が求められる。ここで圧倒的な存在感を示しているのがNTTだ。

NTTは、長年の通信インフラで培った高周波制御技術を応用し、量子チップの近傍(極低温環境下)に配置される「進行波型パラメトリック増幅器(TWPA)」をはじめとする超低ノイズ増幅器の開発で世界をリードしている。これにより、ノイズフロアに埋もれがちな量子ビットの読み出し信号を、量子力学的な限界に近い低ノイズで増幅することが可能になり、エラー訂正に不可欠な「高速・高忠実度な状態測定」を強力にバックアップしている。

一方、情報通信研究機構(NICT)や関連大学は、次世代インフラへと昇華させる「分散型量子ネットワーク」の構築を推進している。単一の希釈冷凍機内に数万ビットを詰め込むアプローチには物理的な限界があるため、マイクロ波領域で動作する超伝導量子ビットの量子状態を、長距離伝送に適した「通信波長帯の光子」にアップコンバージョン(波長変換)するハイブリッド技術の開発が進められている。これが実現すれば、複数拠点にある国産量子コンピュータを光ファイバー網でセキュアに結合し、あたかも1つの巨大な量子計算機として機能させるスケーラブルなシステムが完成する。

産学連携の課題と次世代サプライチェーンの構築

しかし、日本国内のエコシステムが手放しで安全圏にあるわけではない。技術が研究室から産業界へ移行する中で、最大の課題となっているのが「量子ソフトウェアエンジニアおよびシステムインテグレーターの圧倒的な不足」と「サプライチェーンの海外依存」である。

現在、ハードウェアを稼働させるための希釈冷凍機はフィンランドのBlueforsなどの海外企業が圧倒的シェアを握っており、極低温同軸ケーブルや特殊なマイクロ波コンポーネントも多くを輸入に頼っている。日本が真の技術的独立性を保ち、グローバル市場における優位性を確立するためには、国境を越えたオープンイノベーションを推進しつつも、部材メーカーや制御ミドルウェアを開発する国内スタートアップへの集中的な資本投下が不可欠である。ハードとソフトの境界領域(コンパイラ、制御最適化)を埋めるプレイヤーの育成こそが、ガラパゴス化を防ぐ生命線となる。

実用化への最大の壁:技術的課題(エラー・スケーラビリティ)の最前線

実機の公開やクラウド経由でのアクセス提供は偉大な一歩であるが、企業のR&D部門やビジョナリーな投資家たちが次に注視すべきは、「稼働する実機」から、真に社会課題を解決できる「実用機(FTQC:誤り耐性量子計算機)」へと至る途方もない技術的ギャップの正体である。理論上のエラー率が改善しても、実デバイスの集積化に伴い想定外の障壁が次々と立ちはだかっている。本セクションでは、いかにしてノイズを抑制し、数万規模へとスケールさせていくのか、エンジニアリングの最前線に迫る。

量子ビット寿命と高精度操作のトレードオフをどう突破するか

量子情報処理を実用レベルに引き上げるための至上命題は、計算の「賞味期限」であるコヒーレンス時間の延長だ。前述した界面のTLS(二準位系)ノイズを克服するため、材料科学の最前線では革新的なアプローチが進んでいる。

従来のアルミニウム(Al)やニオブ(Nb)に代わり、近年世界中の研究室でブレイクスルーとなっているのが、表面酸化膜の品質が安定し、誘電体損失が劇的に少ない「タンタル(Ta)」をベース材料として採用するアプローチだ。最新のR&Dデータでは、これによりコヒーレンス時間が従来の数十マイクロ秒から、一気に300〜500マイクロ秒の領域へと跳ね上がる成果が報告されている。また、マイクロ波の制御パルス波形を機械学習で最適化し、ノイズ周波数を動的に回避するソフトウェアレベルのデカップリング技術も実用化されつつある。

しかし、設計現場を悩ませるのは「周波数衝突(Frequency Collision)」と「操作速度のトレードオフ」である。コヒーレンス時間を延ばすために外部環境との結合を弱めると、2量子ビットゲートの操作時間が延び、結果としてその間に別の熱ノイズや位相エラーが混入する。また、製造時のジョセフソン接合の膜厚バラツキにより、隣接する量子ビットの共振周波数が意図せず一致してしまい、クロストーク(信号干渉)が発生する問題も深刻である。現在、この課題に対しては、ゲート操作時のみ結合をオンにする「可変結合器(Tunable Coupler)」の高度な回路設計が標準装備となりつつある。

量子エラー訂正(QEC)と表面符号実装の「オーバーヘッド問題」

ハードウェアの寿命延長だけでは限界があり、絶対的に不可欠となるのが量子エラー訂正(QEC: Quantum Error Correction)技術である。超伝導方式における代表的なQEC手法は、2次元平面上に物理ビットを配列する「表面符号(Surface Code)」であるが、ここには「オーバーヘッド」という極めて重い課題が存在する。

表面符号を用いて、エラーのない「論理量子ビット(Logical Qubit)」を1つ構築するためには、エラーを検知・補正する「シンドローム測定」のために数百から数千の物理量子ビットを割り当てる必要がある。さらに、特定の複雑なゲート操作(Tゲートなど)を実行するためには「マジックステート蒸留(Magic State Distillation)」という膨大なリソースを消費するプロセスが必要となり、実用的なアルゴリズムを回すには最終的に数百万の物理ビットが必要と試算されている。

さらに近年、表面符号の前提を根底から覆しかねない脅威として特定されたのが「宇宙線や自然放射線による相関エラー(Correlated Errors)」である。高エネルギー粒子が量子チップの基板(シリコン等)に衝突すると、フォノン(格子振動)が広範囲に伝播し、複数の量子ビットが「同時に」エラーを起こす。表面符号は「エラーは独立してランダムに起きる」という前提で設計されているため、この同時多発エラーには対処しきれない。現在、基板にフォノンを吸収するシンク(金などの金属層)を設けたり、ディープエッチングでチップを物理的に分離したりする等の泥臭いハードウェア改修が急ピッチで進められている。

冷却インフラと配線の限界を突破する:極低温CMOSと3D実装技術

数百万の量子ビットを集積する上で、チップの面積以上に致命的なボトルネックとなるのが「配線と熱流入の限界(Wiring Bottleneck)」である。現在のアーキテクチャでは、室温の制御機器から極低温(約15mK)の量子チップへ、同軸ケーブルを1対1(あるいは1対複数)で物理的に配線している。ビット数が数千を超えれば、ケーブルの物理的スペースと、金属線を伝わって流入する熱量が希釈冷凍機の冷却能力(典型的には数百マイクロワット程度)を優に超えてしまう。

この絶望的な壁を突破するための切り札が「クライオCMOS(極低温動作IC)」と「3次元実装(3D Integration)」だ。

- クライオCMOS制御: 室温の機器に頼るのではなく、4K(ケルビン)といった比較的冷却能力に余裕のある温度帯に、マイクロ波を生成・多重化する専用のCMOS集積回路を配置する。これにより、室温から極低温へ向かうケーブルの数を劇的に(数十分の一に)削減する。

- 3次元実装とTSV: 量子ビットが並ぶチップと、読み出し回路や制御配線を担うチップを分け、フリップチップボンディングやTSV(シリコン貫通電極)を用いて垂直に積層する。これにより、平面上の配線混雑を解消し、無限に近い2次元スケーラビリティを確保する。

これらの技術的ブレイクスルーが揃って初めて、超伝導方式は競合技術を突き放し、真の大規模化への扉を開くことになる。

投資家・CTO必見:超伝導量子技術の産業インパクトと未来ロードマップ

超伝導量子技術は、「基礎研究のフェーズ」から「産業実装とサプライチェーン構築のフェーズ」へと完全に移行した。このセクションでは、超伝導回路の集積化とエラー訂正の進展が、今後10〜20年でどの産業に破壊的イノベーションをもたらすのか、その経済的波及効果と投資戦略を提示する。

2026〜2030年の予測シナリオ:NISQ後期からアーリーFTQCへの移行

2020年代後半から2030年にかけて、業界の焦点は「単なる物理ビット数の競争」から「論理量子ビットの生成と制御」へとシフトする。現在主流のノイズを伴うNISQ(中規模量子デバイス)時代においては、エラーをソフトウェア的に相殺する「エラー抑制(Error Mitigation)」技術が極限までチューニングされる。

そして2026〜2030年の予測シナリオとして最も現実的なのは、数十〜数百の物理ビットを用いて、数個から十数個のエラーのない「論理量子ビット」を実証する「アーリーFTQC(Early-FTQC)」の実現である。この段階では、まだ数百万ビットを要する完全な暗号解読(Shorのアルゴリズム)などは不可能だが、一部の高度な素材シミュレーションにおいて、古典スーパーコンピュータ(HPC)を凌駕する「量子的優位性(Quantum Advantage)」が明確な商業的価値として証明されるだろう。超伝導方式はゲート速度の速さゆえに、この「限られた論理ビットでの高速演算テスト」において最も有利なポジションにいる。

企業R&Dが備えるべき技術戦略とユースケースの開拓

企業のCTOやR&D部門は、数百万ビットの完全なFTQCの完成を待つのではなく、現在のアーリーFTQCに向けた過渡期のハードウェア制約を理解した上で、戦略的な技術検証(PoC)を直ちに開始すべきである。

| 時期 | 技術フェーズとハードウェア要件 | ターゲット産業・変革されるキラーユースケース |

|---|---|---|

| 2025〜2030年 | エラー抑制技術の成熟とアーリーFTQC 1,000〜10,000物理量子ビット |

【素材・化学】特定の小分子や触媒の基底状態エネルギー計算。VQE(変分量子固有値ソルバー)の限界を超え、浅い回路でのQPE(量子位相推定)の軽量版の実装。次世代バッテリー固体電解質の初期シミュレーション。 |

| 2030〜2035年 | 初期FTQC(論理量子ビットの実用化) 1万〜10万物理量子ビット |

【金融・物流】量子エラー訂正の小規模実装により計算精度が飛躍。複雑なサプライチェーン網の即時最適化、モンテカルロ法を加速させる高度な金融デリバティブのリアルタイムリスク計算。 |

| 2035年以降 | 大規模FTQCの実用化 100万以上の物理量子ビット |

【創薬・エネルギー】新薬候補化合物の完全な分子シミュレーション(創薬プロセスの年単位での短縮)、常温超伝導材料の探索による送電ロスの撤廃、カーボンニュートラルに向けた高効率な二酸化炭素吸着材の設計。 |

企業R&Dが取るべき具体的なアクションは、クラウド経由でアクセス可能な国産量子コンピュータを活用し、「自社のドメイン知識(化学方程式や金融モデル)を、いかにノイズに強い量子アルゴリズムへと変換するか」のノウハウを蓄積することである。アルゴリズムそのものや、古典HPCとの最適なワークフロー分割(量子古典ハイブリッド)に関する特許取得が、当面の最重要KPIとなる。

ディープテック投資から見る次世代周辺技術の勝機と市場予測

ディープテック投資家にとって、超伝導量子技術の市場は、GoogleやIBMのような「フルスタックシステム」を開発する巨大企業への投資に留まらない。むしろ、莫大なリターンをもたらす真の投資機会は、スケーラビリティの壁を突破するための「ピックス・アンド・ショベル(周辺ツールや部材)」を担う次世代サプライチェーンに潜んでいる。

- 極低温コンポーネントと配線技術: 先述したクライオCMOS、極低温環境での熱流入を極限まで抑える超伝導同軸ケーブル、ノイズレスな増幅器(TWPA)などの需要は爆発的に増加する。現在一部の海外企業が寡占しているこの領域において、国内の精密部品メーカーや高周波技術を持つスタートアップには数千億円規模のゲームチェンジの機会がある。

- 量子ファウンドリと専用製造装置: ジョセフソン接合の酸化膜厚をオングストローム(100億分の1メートル)単位で均一に制御し、クロストークを防ぐための専用成膜装置やエッチング装置の開発。歩留まりを飛躍的に向上させる「量子チップ専用ファウンドリビジネス」は、既存の半導体エコシステムとは異なる新たな市場を形成する。

- ハードウェア抽象化・コンパイラミドルウェア: ハードウェアごとに異なるノイズ特性やクロストークマップをリアルタイムに学習し、量子アルゴリズムを最も効率的な物理パルスへと自動変換(コンパイル)するミドルウェア層。ハードウェアの物理的欠陥をソフトウェアで隠蔽するこのレイヤーを制する企業が、量子時代のOS(オペレーティングシステム)としての地位を確立するだろう。

超伝導方式の大規模化と完全な量子エラー訂正の実現は、単独のテックジャイアントだけで完結するものではない。極低温技術、高周波制御、ナノファブリケーション、そしてミドルウェアという異業種のエッジ技術を巻き込んだ強固なエコシステムをいかに迅速に構築できるかが、グローバル市場における競争優位性を決定づける最大のファクターとなる。

よくある質問(FAQ)

Q. 超伝導量子ビットとは何ですか?

A. 超伝導量子ビットは、極低温に冷却した超伝導回路と「ジョセフソン接合」を用いて作られる人工原子を利用した量子計算の方式です。GoogleやIBMといった巨大テック企業のほか、日本の国産量子コンピュータ初号機「叡」でも採用されており、現在の量子ハードウェア開発におけるメインストリームとなっています。

Q. 超伝導量子コンピュータの実用化はいつですか?

A. 誤り耐性量子計算(FTQC)が可能となる本格的な実用化は、2030年代と予測されています。実現に向けては、極低温環境での熱力学的限界や、デコヒーレンス(状態の崩れ)などのエラーを克服する必要があります。現在は量子エラー訂正(QEC)技術の確立に向けたシビアな研究開発が最前線で進められています。

Q. 超伝導量子ビットと他の方式(イオントラップや光など)の違いは何ですか?

A. 超伝導方式は既存の微細加工技術を応用しやすく拡張性に優れる反面、極低温環境でのシビアな熱管理やエラー対策が必要です。一方、イオントラップや冷却原子方式は量子ビットの寿命が長く高品質ですが大規模化に課題があります。光方式は常温動作が可能など、各方式で優位性と技術的限界(トレードオフ)が異なります。