生成AIの急速な進化と大規模言語モデル(LLM)のパラメータ数の爆発的な増加により、半導体業界はかつてない激動の時代を迎えています。これまで半導体の性能向上を牽引してきた「ムーアの法則」に基づく前工程(フロントエンド)の微細化は、物理的な限界と天文学的な開発コストの壁に直面しています。このパラダイムシフトの中、AIチップの演算性能、消費電力、そして歩留まり(製造成功率)を最終的に決定づける最重要技術として急浮上したのが、後工程(バックエンド)における「先端パッケージング」技術です。

本記事では、現在のAI半導体市場において事実上の業界標準(デファクトスタンダード)として君臨し、世界のテクノロジー覇権を左右するTSMCの2.5Dパッケージング技術「CoWoS(Chip-on-Wafer-on-Substrate)」について、その根底にある技術アーキテクチャから、直面する物理的・熱力学的な課題、競合技術との比較、そして2026〜2030年を見据えた次世代ビジネスシナリオまで、徹底的に深掘りして解説します。

- AI時代の覇権を握る「CoWoS」とは?基礎知識と注目される背景

- CoWoSの定義と2.5Dパッケージングにおける位置付け

- チップレットとHBM3がもたらすAI半導体へのパラダイムシフト

- CoWoSの技術アーキテクチャと3つの進化系(S / R / L)

- シリコン貫通電極(TSV)とインターポーザが支える基本構造

- 用途で分かれる「CoWoS-S・R・L」の性能とコスト比較

- レチクル限界と熱問題:次世代パッケージングが直面する壁と競合比較

- 大型化するインターポーザと微細化の物理的限界(レチクル限界)

- 放熱課題を克服するハイブリッドボンディング技術と競合比較

- 歩留まりと信頼性を左右する「評価・解析」の重要性

- 複雑な3D構造に潜む熱ストレスと接続不良リスク

- 量産化の壁を越える高度な故障解析とAI駆動のテスト手法

- TSMCの戦略とサプライチェーンの地殻変動

- AI半導体需要の爆発による供給不足とTSMCのキャパシティ拡大

- 「前工程」から「後工程」へシフトする半導体業界の付加価値

- 2026〜2030年予測:日本企業の勝機と今後の投資・ビジネスシナリオ

- 先端パッケージングを裏で支える日本の「材料・製造装置」エコシステム

- テック投資家と事業開発者が注視すべき次世代ロードマップ

AI時代の覇権を握る「CoWoS」とは?基礎知識と注目される背景

CoWoSの定義と2.5Dパッケージングにおける位置付け

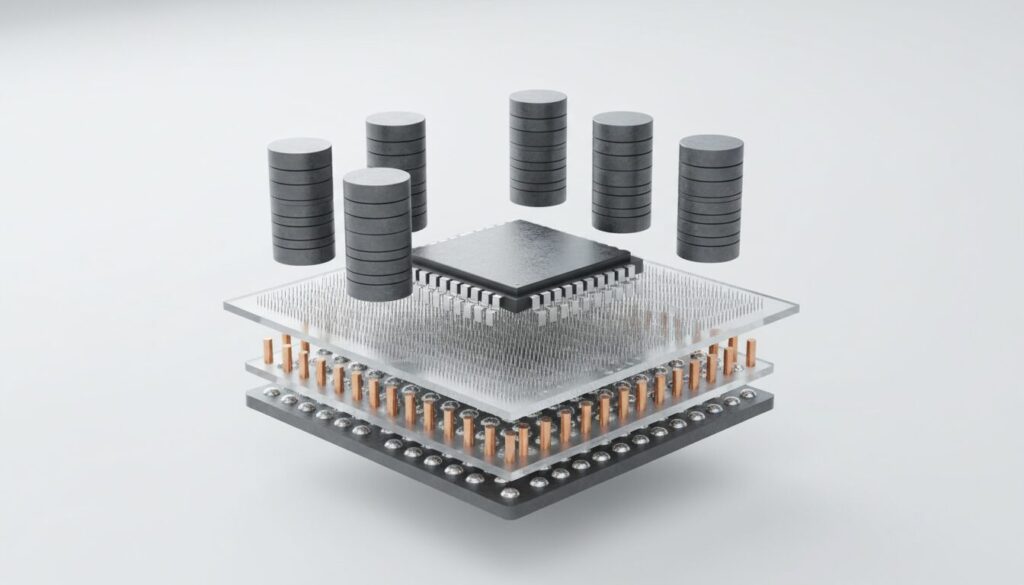

CoWoS(Chip-on-Wafer-on-Substrate)とは、台湾のファウンドリ最大手であるTSMCが開発し、現在AI半導体市場において事実上の業界標準となっている最先端の2.5Dパッケージング技術です。表面的な定義としては、「有機基板(Substrate)の上に、シリコン等で形成されたインターポーザ(中間基板)を配置し、その上に複数の半導体チップを超高密度で近接実装する技術」となります。

CoWoSの歴史は古く、2012年にXilinx(現AMD)のハイエンドFPGA向けに初めて実用化されました。しかし、半導体業界の最前線や投資の現場において、現在のCoWoSは単なる「後工程の新しい組み立て手法」としては語られません。それは、ムーアの法則の鈍化を補い、半導体性能の物理的限界を突破するための「ゲームチェンジャー」として再定義されています。近年、最先端のEUV(極端紫外線)露光装置が一度のプロセスで焼き付けられる回路面積の物理的な上限であるレチクル限界(約858平方ミリメートル)が、数千億から数兆のパラメータを処理する巨大なAIチップ開発において致命的な障壁となっていました。

2.5Dパッケージングは、このレチクル限界を実質的に無効化する画期的なアプローチです。インターポーザを介してチップ間の超微細な配線を可能にすることで、複数の独立したチップをあたかも一つの巨大なモノリシック(単一)ダイであるかのように同期・連携動作させることができます。

現在、TSMCは顧客の要求性能やコスト構造に応じて、CoWoS-S、CoWoS-R、CoWoS-Lという3つの主要なファミリーを展開しており、これが世界の半導体サプライチェーン全体に巨大な波及効果をもたらしています。今日、NVIDIA製GPUをはじめとするAI半導体の世界的な供給ボトルネックは、チップそのものの「微細化(前工程)」ではなく、圧倒的に「CoWoSの生産キャパシティ(後工程)」に起因しています。製造装置メーカーや材料サプライヤーにとって、TSMCの先端パッケージングへの設備投資動向は数兆円規模の市場機会を左右するものであり、アナリストが四半期決算で最も注視する指標となっています。

チップレットとHBM3がもたらすAI半導体へのパラダイムシフト

CoWoSがもたらしたビジネスと技術における最大のパラダイムシフトは、チップレット構想の完全な実用化です。従来のように巨大なチップを単一のシリコンウェハーから切り出す手法では、製造中に生じる微小なダストや欠陥が一つあるだけでチップ全体が不良品となり、製造コストが天文学的に跳ね上がっていました。

チップレット技術では、巨大な回路を機能ごとに小さなダイ(チップレット)に分割して製造し、CoWoS上で再結合します。これにより歩留まりが劇的に改善されるだけでなく、「高度な演算が求められるAIコアは最先端の3nmプロセスで、シンプルなI/O制御回路やSRAMはコストの安い成熟した6nmや7nmプロセスで製造する」といった異種ノードのハイブリッド集積(ヘテロジニアス・インテグレーション)が可能となり、開発・製造コストの抜本的な最適化が実現しました。

さらに、生成AIの台頭により直面した最大の技術的ハードルが「メモリの壁(Memory Wall)」と「電力の壁(Power Wall)」です。演算器(GPU)の処理能力が飛躍的に向上しても、データが格納されているメモリとの間の転送速度が遅ければ、AIの学習・推論性能は頭打ちになります。この限界を打ち破るのが、広帯域メモリであるHBM3(High Bandwidth Memory 3)やその後継規格であるHBM3E/HBM4と、CoWoSの強力なシナジーです。

CoWoSのインターポーザ技術を用いることで、GPUコアの周囲にHBMを最短距離かつ超高密度な配線で配置でき、テラバイト/秒(TB/s)クラスという驚異的なデータ転送帯域を、極めて低い消費電力で実現しています。

| 評価軸 | 従来型(モノリシックアーキテクチャ) | CoWoS + チップレット + HBM の最新構成 |

|---|---|---|

| チップサイズの限界 | レチクル限界(約858mm²)で頭打ちとなり拡張困難 | レチクル限界の数倍規模(3倍〜5倍以上)まで論理的に拡張可能 |

| メモリ帯域幅 | パッケージ外の汎用メモリ接続(GDDR等)のため数百GB/s止まり | インターポーザ経由の至近距離接続により数TB/sの超広帯域を実現 |

| 歩留まりとコスト | 巨大ダイは欠陥リスクが指数関数的に高く、歩留まりが極端に悪化 | 小分割化により高歩留まりを維持し、異種プロセスの混載でコスト最適化 |

| 技術の発展方向 | トランジスタの微細化(前工程)に強く依存 | 先端パッケージング技術(後工程)がシステム全体の性能を牽引 |

CoWoSの技術アーキテクチャと3つの進化系(S / R / L)

AI半導体の急激な性能向上を根底から支え、現代のコンピューティングのボトルネックを解消するTSMCの2.5Dパッケージング技術「CoWoS」。本セクションでは、その概念的な理解から一歩踏み込み、最前線の技術アーキテクチャと内部構造を徹底解剖します。投資家や半導体エンジニアが注目すべきは、単なる配線の高密度化に留まらず、「熱・電気的特性の極限の最適化」と「製造コスト・スケーラビリティのトレードオフ」をいかに高次元で制御しているかという点にあります。

シリコン貫通電極(TSV)とインターポーザが支える基本構造

CoWoSアーキテクチャの心臓部を成すのが、ロジックダイとメモリダイの直下に配置されるインターポーザ(中間基板)です。従来の有機パッケージ基板の配線ルール(ライン/スペースが数十ミクロンレベル)では不可能だった、ナノメートルオーダーの超高密度な配線(ルーティング)を可能にし、各ダイ間のデータ転送帯域を飛躍的に向上させています。

このインターポーザの内部において、垂直方向の電気的導通と電力供給を担う要となるのがシリコン貫通電極(TSV:Through-Silicon Via)です。微細な孔をシリコン層に深掘りエッチング(DRIE等を使用)で開け、そこに銅などの導電性材料を電解メッキで充填するこの技術により、ミリ秒以下のレイテンシを争うAI演算において、最短距離での信号伝送を実現します。

さらに、ダイとインターポーザを物理的かつ電気的に接合するマイクロバンプ(微小なはんだ突起)は、現在30〜40ミクロンピッチまで微細化が進行しています。巨大なモノリシックダイの製造が歩留まりの観点で限界を迎える中、複数の機能別小規模チップを組み合わせるチップレット技術を実装する上で、インターポーザとTSVは不可欠な「キャンバス」として機能しているのです。

用途で分かれる「CoWoS-S・R・L」の性能とコスト比較

TSMCは、顧客の多様なアプリケーション要件とプロダクト戦略に応えるため、CoWoSを主に3つの進化系に分岐させました。これらは使用するインターポーザの素材や構造設計によって分類され、性能上限、製造コスト、そしてパッケージの最大面積に明確な差異をもたらしています。

- CoWoS-S (Silicon): シリコンウェハーそのものをインターポーザとして使用する、最も実績のある王道アーキテクチャです。シリコン由来の極めて微細な配線(前工程の露光装置を使用可能)による最高クラスの性能を誇り、NVIDIAのH100などのフラッグシップAI-GPUに採用されています。しかし、シリコン製造装置の露光面積の限界であるレチクル限界の制約を強く受けます。

- CoWoS-R (RDL): シリコンの代わりに、有機材料を用いた再配線層(RDL:Redistribution Layer)を採用する構造です。高価なシリコンウェハーや複雑なTSV工程を使用しないため、極めてコスト競争力が高く、柔軟な大面積化が容易です。有機材料は誘電率が低いため高速信号伝送時のノイズ(RC遅延)を低減できるメリットもあり、ネットワークスイッチ回路やミドルレンジのエッジAI向けチップに最適化されています。

- CoWoS-L (Local Silicon Interconnect): 「S」の圧倒的な帯域性能と「R」のコスト優位性・大面積化のメリットを融合(いいとこ取り)した最新アーキテクチャです。安価なモールド樹脂ベースの基板の中に、チップ間を接続する超高密度配線が必要な局所部分にだけ、小型のシリコンブリッジ(LSI)を埋め込みます。これにより、レチクル限界を突破し、レチクルサイズの3.3倍〜将来的には6倍超という広大なパッケージ領域を構築しつつ、高価なシリコンの使用面積を最小化してコストを劇的に抑えることが可能になります。

ここで特筆すべきは、Intelが提唱する「EMIB(Embedded Multi-die Interconnect Bridge)」との競合関係です。EMIBも同様に局所的なシリコンブリッジを使用する技術ですが、CoWoS-LはTSMCの卓越したモールディング(樹脂封止)技術と組み合わせることで、より高い量産安定性とエコシステムの強固さを実現しており、次世代AIチップ(NVIDIA B200等)のデファクトスタンダードの座を勝ち取っています。

レチクル限界と熱問題:次世代パッケージングが直面する壁と競合比較

ここまでは先端パッケージングがもたらすAI半導体の性能向上メカニズムを見てきましたが、ここからは技術的な「落とし穴」と次世代の解決策にフォーカスします。生成AIの爆発的普及により、チップレットアーキテクチャの高度化とHBMの搭載数増加は止まることを知りません。しかし、この進化は製造プロセスにおいて「面積」と「熱」という2つの巨大な壁に直面しています。

大型化するインターポーザと微細化の物理的限界(レチクル限界)

現在の2.5Dパッケージングにおいて、複数のロジックダイやメモリを繋ぐインターポーザの巨大化は避けて通れません。NVIDIAの次世代GPUやAMDの最新AIアクセラレータでは、搭載されるHBMの数が6個、8個と増加しており、これを支えるためのインターポーザは肥大化の一途を辿っています。

一般的な半導体露光装置(ステッパー/スキャナー)が1回のショットで転写できる最大面積は、約858平方ミリメートル(26mm × 33mm)と物理的に決まっています(レチクル限界)。最新のAIチップではこのレチクル面積の3〜4倍(約2,500〜3,000平方ミリメートル超)を要求する設計が登場しています。TSMCは、露光領域を分割して高精度に繋ぎ合わせる「ステッチング技術」を用いて巨大なシリコンインターポーザを製造してきましたが、面積が大きくなるほど歩留まり(イールド)は指数関数的に低下し、コストは跳ね上がります。

このレチクル限界の壁を突破するため、TSMCは前述のCoWoS-Lの量産を急ピッチで進めています。さらに2026年以降の長期シナリオとして、有機基板よりも圧倒的に平滑で剛性が高く、微細配線が可能な「ガラス基板(Glass Core Substrate)」の導入に向けた研究開発が業界全体で加速しています。ガラス基板は巨大化するパッケージの反りを防ぐ究極のソリューションとして、Intelなども強力に推進しています。

放熱課題を克服するハイブリッドボンディング技術と競合比較

面積の壁と同時に深刻化しているのが「熱問題」と「信号遅延」です。高性能なロジックダイとHBMを限界まで近接・積層させる実装では、電力密度の急増により局所的なホットスポットが発生します。これまでの実装では、ダイとインターポーザの接続に微小なはんだバンプとTSVが使用されてきましたが、バンプレベルでの寄生容量や熱抵抗が、次世代の広帯域データ転送と熱排出の足を引っ張るようになっています。

この限界を打破するゲームチェンジャーとして、現在最も注目を集めているのがハイブリッドボンディング(Cu-Cu直接接合)技術です。はんだバンプを完全に排除し、銅の電極同士を分子間力で直接結合させるこの技術は、パッケージング業界の真のパラダイムシフトを意味します。

| 比較項目 | 従来のマイクロバンプ接続 | ハイブリッドボンディング技術 |

|---|---|---|

| 接続ピッチ(端子間隔) | 30〜40マイクロメートルが限界 | 10マイクロメートル以下(数μmまで縮小可能) |

| 信号帯域・電力効率 | バンプの寄生容量・抵抗により高周波数帯でロス発生 | バンプレスにより寄生容量が激減、圧倒的な広帯域と低消費電力を実現 |

| 熱放散性能(熱抵抗) | アンダーフィル樹脂やバンプが断熱層となり熱が籠もりやすい | シリコンと銅が直接接合されるため、熱伝導パスが最短化され放熱性が飛躍的に向上 |

| 製造難易度と装置要件 | 既存のフリップチップ実装技術の延長で対応可能 | ナノレベルの超平坦化(CMP)、プラズマ活性化、超高精度アライメント装置が必須 |

TSMCは「SoIC(System on Integrated Chips)」という名称でハイブリッドボンディングを実用化しており、Intelの「Foveros Direct」やSamsungの「X-Cube」と激しい技術覇権争いを繰り広げています。SoICは次世代アーキテクチャにおいてCoWoSプラットフォームと統合される見通しであり、HBMの多段積層(12段、16段)における熱のボトルネックをクリアしつつ、I/O帯域を現在の数倍にまで引き上げることが可能です。

さらに2028年以降を見据えた予測シナリオとして、基板上の電気配線を光信号に置き換えて発熱を根本から絶つCPO(Co-Packaged Optics:光電融合技術)の実装が控えており、パッケージング技術は物理学の限界に挑む総合工学へと進化しています。

歩留まりと信頼性を左右する「評価・解析」の重要性

複雑な3D構造に潜む熱ストレスと接続不良リスク

TSMCが牽引する先端パッケージング技術は、微細な3D接続の歩留まり確保という未曾有の製造課題に直面しています。巨大なロジックダイと複数のHBMを極小ピッチで同一基板上に統合する環境下では、製造工程における熱ストレスが引き起こす物理的破壊が極めて深刻なリスクとなります。

最大の障壁となるのが、チップレット、インターポーザ、パッケージ基板がそれぞれ異なる熱膨張係数(CTE:Coefficient of Thermal Expansion)を持っている点です。リフロー(はんだ付け)工程における加熱・冷却のサイクルで生じる熱収縮の差は巨大な応力を生み出し、パッケージ全体に深刻な反り(Warpage)を引き起こします。面積の拡大は反り応力を指数関数的に増大させ、以下の接続不良リスクを誘発します。

- マイクロバンプのクラックと断線: 数万から十数万個に及ぶ微細なはんだバンプの一部に応力が集中し、オープン(断線)またはショート(短絡)不良を誘発します。

- シリコン貫通電極(TSV)のボイドと剥離: TSV内部に充填された銅(Cu)と周囲のシリコンのCTEミスマッチにより、熱サイクル試験中に界面剥離(デラミネーション)やマイクロボイドが発生し、信号の完全性が失われます。

- エレクトロマイグレーションの加速: HBMとロジック間の超高速通信に伴う高電流密度と局所的な発熱が、バンプ内の金属原子を移動させ、長期的なデバイス信頼性を著しく損ないます。

量産化の壁を越える高度な故障解析とAI駆動のテスト手法

最終工程で単体数十万円にも達する高価なAI半導体をパッケージごと廃棄するコストロスを防ぐため、製造プロセスの各段階における「評価・解析」と「テスト手法」の高度化が不可欠です。チップレット時代のテストパラダイムは、単一ダイの良否判定から「パッケージ全体の協調テストとインターコネクト評価」へと劇的にシフトしています。

量産現場の最前線では、以下のような高度な解析・テスト手法が統合され始めています。さらに近年では、テストデータと製造装置のパラメータを機械学習(AI)で紐づけ、不良発生を未然に防ぐ「AI駆動の歩留まり予測」が実装されつつあります。

| 評価・テスト手法 | 対象・目的 | 実務・投資への技術的インパクト |

|---|---|---|

| 3D X線CT / 超音波探傷(C-SAM) | パッケージ内部の非破壊検査 | TSVやバンプに潜む内部ボイド・クラックを出荷前に非破壊で検出。インラインでの高速検査能力が装置メーカーの競争力に直結。 |

| FIB-SEMによる断面観察・解析 | ナノレベルの接合界面解析 | 故障原因を原子レベルで特定し、ハイブリッドボンディングやCoWoS-Lのプロセス改善ループを高速化。R&Dの成否を分ける。 |

| KGD / KGS スクリーニング | 組み立て前の良品保証テスト | KGD(Known Good Die)およびKGS(良品インターポーザ)を厳密に選別し、組み立て後のパッケージ全損リスクを排除。廃棄コストを激減させる。 |

| システムレベルテスト(SLT) | 実動作環境下での最終テスト | HBMの広帯域データ転送や熱動態を実機に近い環境でストレステストし、データセンターでの長期信頼性を担保。ATEメーカーへの巨大な特需を生む。 |

TSMCの戦略とサプライチェーンの地殻変動

AI半導体需要の爆発による供給不足とTSMCのキャパシティ拡大

NVIDIAのGPUをはじめとする生成AIインフラ整備が世界的な熱狂を帯びる中、投資家やアナリストが直視すべき真のボトルネックは最先端ロジック(3nm等)の前工程製造能力ではなく、2.5Dパッケージング技術であるCoWoSのキャパシティ不足です。

このボトルネックを解消するため、TSMCは異例のスピードで台湾国内の先端パッケージング専用工場(AP6など)へ設備投資を拡大しています。2023年時点で月産1万枚強と推定されたCoWoSのウェハ処理能力を、2024年末までに約3万枚強へと引き上げ、2025年にはさらに倍増させる野心的な拡張計画が進行中です。

さらに、自社のキャパシティだけでは爆発的な需要を賄いきれないため、TSMCはAmkor TechnologyやASE(Advanced Semiconductor Engineering)などの世界的な大手OSAT(後工程受託製造企業)に対し、CoWoSプロセスの一部である「oS(on Substrate:インターポーザと基板の接合工程)」を委託するなど、これまで内製中心だったサプライチェーンの境界線を柔軟に開放し始めています。これにより、ファウンドリとOSAT間の新たなエコシステム協業モデルが構築されています。

「前工程」から「後工程」へシフトする半導体業界の付加価値

かつては「いかに微細なトランジスタをシリコンウェハ上に焼き付けるか」という前工程のみが付加価値(利益率)の源泉とされてきました。しかし、ムーアの法則の減速に伴い、その覇権は完全に先端パッケージング技術へとシフトしています。

TSMCは、高度な2.5D/3Dパッケージング技術を「3DFabric」という包括的なプラットフォームとして体系化し、チップ設計の初期段階から顧客を巻き込む「パッケージ・レベル・コデザイン(Co-Design)」を提唱しています。EDA(電子設計自動化)ツールベンダーと連携し、熱シミュレーションや応力解析を含めた設計環境(OIP:Open Innovation Platform)を提供することで、TSMCのエコシステムから顧客が離脱できない強力なロックイン(囲い込み)を実現しています。

前工程の微細化が限界に近づく中、後工程をブラックボックス化しシステムレベルのインテグレータへと進化したTSMCの戦略こそが、現代の半導体産業における「後工程を制する者が市場を制する」というテーゼを体現しています。

2026〜2030年予測:日本企業の勝機と今後の投資・ビジネスシナリオ

先端パッケージングを裏で支える日本の「材料・製造装置」エコシステム

TSMCの圧倒的な市場シェアの根底にあるサプライチェーンを紐解くと、日本の材料・製造装置メーカーが不可欠なキープレイヤーとして君臨していることがわかります。投資家や事業開発担当者は、フロントエンドの微細化競争だけでなく、パッケージング領域の技術革新にこそ次の巨大なキャピタルゲインの源泉を見出すべきです。

日本のエコシステムは、物理的・化学的限界を突破するためのコア技術を独占的に供給しています。

- 最先端絶縁材料と封止材(モールド樹脂): 巨大なインターポーザ上にチップレットを集積する際、熱による反り(Warpage)の制御が致命的な課題となります。ここで圧倒的シェアを誇るのが、味の素ファインテクノのABF(ビルドアップフィルム)や、レゾナック、住友ベークライトが手掛ける高放熱・低熱膨張のアンダーフィル材・モールディング樹脂です。

- 超精密ダイシングと薄化装置: ディスコに代表される日本の研削・切断技術は、極限まで薄化されたHBMの多段積層プロセスにおいて、チップクラックを防ぎ歩留まりを劇的に改善しています。

- 高度な検査・テストソリューション: アドバンテストをはじめとするテスト装置メーカーは、マルチチップ化によって複雑を極めるKGDの保証において、テストコストの最適化とAIドリブンの予測技術を提供しています。

一方で、韓国や中国のローカルサプライヤーによる激しいキャッチアップ(国産化代替)も進行しており、日本企業は常に「次の世代の素材・装置」を先行して市場に投入し続ける技術的優位性の維持が求められます。

テック投資家と事業開発者が注視すべき次世代ロードマップ

今後のエコシステムは、マイクロバンプを介した接合から、銅と銅を直接結合するハイブリッドボンディングへ、そして基板材質の抜本的な見直しへとパラダイムシフトを起こします。事業開発者や投資家がベンチマークとすべき、2026年から2030年に向けた次世代の技術ロードマップは以下の通りです。

| フェーズ | ターゲット技術・製品 | 技術的課題とビジネスインパクト | 注目の日本企業・技術領域 |

|---|---|---|---|

| 現在〜2026年 | CoWoS-Lの普及とHBM3Eの統合 | レチクル限界の3〜4倍を超える巨大パッケージの歩留まり向上。熱放散と基板の反り制御が急務。 | 超低熱膨張モールド樹脂、2.5D向け高精度ダイボンダ、KGDテスト装置 |

| 2026年〜2028年 | 次世代「ガラス基板」の台頭とHBM4の直接積層 | 有機基板の平滑性限界とシリコンインターポーザのコスト限界を打開するため、ガラス基板(Glass Core)の商用化が開始。 | 大日本印刷(DNP)、イビデン等によるガラス基板製造、ガラス向けレーザー穴あけ装置(TGV) |

| 2028年〜2030年 | ハイブリッドボンディング本格量産とCPO(光電融合) | ナノレベルの平坦性(CMP)と超清浄環境が必須となり、前工程(ファブ)と同等の装置群が後工程に大量流入。熱問題を光通信で解決。 | 次世代化学機械研磨(CMP)、プラズマ活性化装置、シリコンフォトニクス実装技術 |

このロードマップが示す通り、半導体製造は「前工程の高度な技術要素を後工程(パッケージング)にそのまま持ち込む」フェーズに入っています。特に次世代のガラス基板への移行や、ハイブリッドボンディングの実装に向けた超精密加工・平坦化・洗浄技術は、日本企業が最も得意とする「すり合わせ技術」の独壇場となる可能性を秘めています。

地政学的なリスク分散の観点からも、TSMCが日本国内(つくば市の3DIC研究開発センターや熊本JASM)との連携を深める中、日本国内での強力な後工程エコシステム構築が現実味を帯びています。AI半導体エコシステムの覇権を巡る闘いにおいて、最先端パッケージングの歩留まり向上と量産化の命運を握る日本の材料・装置メーカー群こそが、中長期的なテクノロジー投資の最大のスイートスポットとなるのです。

よくある質問(FAQ)

Q. 先端パッケージング(CoWoS)とは何ですか?

A. 先端パッケージングとは、半導体の製造における「後工程」で複数のチップを高密度に統合する技術です。中でもTSMCが開発した2.5Dパッケージング技術「CoWoS」は、現在のAI半導体市場の事実上の業界標準(デファクトスタンダード)となっており、AIチップの演算性能や消費電力を左右する重要な役割を担っています。

Q. なぜ先端パッケージングが半導体の最重要技術として注目されているのですか?

A. 生成AIの進化に伴い、従来の半導体性能向上を牽引してきた「ムーアの法則」に基づく前工程の微細化が、物理的限界と天文学的な開発コストの壁に直面しているためです。その解決策として、複数のチップ(チップレットやHBM3など)を組み合わせて歩留まり(製造成功率)を高める先端パッケージングが急浮上しました。

Q. CoWoSの技術アーキテクチャ「S・R・L」の違いは何ですか?

A. TSMCのCoWoS技術には、基板の素材や構造によって「S・R・L」の3つの進化系が存在します。主に、シリコンインターポーザを用いた高性能向けの「S」、有機基板でコストを抑えた「R」、局所的な配線層を活用してチップの大型化に対応する「L」に分かれ、AI半導体の要求性能や用途に合わせて選択されます。