現代の半導体産業において、最も劇的な技術革新が進行している領域が「アドバンスド・パッケージング(先進実装)」です。長らく業界を牽引してきた「ムーアの法則」によるトランジスタの微細化は、物理法則の限界と製造コストの異常な高騰という高い壁に直面し、単一のシリコンダイで性能向上を図る時代は事実上の終焉を迎えました。それに代わり、生成AIの爆発的普及やデータセンターの高度化を根底から支え、グローバルなテクノロジー覇権の鍵を握るようになったのが、複数のチップを立体的に統合する「3Dスタッキング(3次元積層)」技術です。本記事では、半導体の付加価値の源泉が「前工程」から「後工程」へとシフトした背景から、ナノレベルの接合技術、立ちはだかる熱・コストの障壁、そして2030年に向けた次世代市場の予測シナリオまで、3D実装技術の全貌を体系的かつ圧倒的な情報量で徹底解剖します。

- 1. 3Dスタッキング(3次元積層)とは?「後工程」が次世代半導体の主役になる理由

- 微細化の限界とAI・5Gが牽引する技術的背景

- 図解でわかる「2.5D実装」と「3D実装」の構造的な違い

- エコシステムの変革と「チップレット」標準化の波(UCIe等の動向)

- 2. 3Dスタッキングを支えるコア接続技術:TSVから最新トレンドまで

- TSV(シリコン貫通電極)とマイクロバンプの基礎と物理的限界

- 次世代の主役「ハイブリッドボンディング」とWOW/COW積層の深掘り

- 最新研究:TSVやバンプの限界を超える「バンプレス積層技術」

- 技術的な落とし穴:ナノレベルの歩留まり管理とテストの壁

- 3. 実装における2大課題(放熱・コスト)と材料技術による解決アプローチ

- 3Dスタッキング最大の障壁「ダークシリコン問題」と熱応力(反り)

- 製造コストの膨張とKGD(良品ダイ)確保のジレンマ

- 課題を克服する「材料選定」:封止材、NCF、次世代TIMの重要性

- 4. チップレット時代の3D実装市場予測と日本の競争優位性

- 2026〜2030年の技術予測シナリオ:光電融合とガラス基板の台頭

- 後工程市場を牽引する国内メーカーの動向と「チョークポイント」の支配

- 経済安全保障とサプライチェーン再構築のインパクト:次世代覇権の行方

1. 3Dスタッキング(3次元積層)とは?「後工程」が次世代半導体の主役になる理由

微細化の限界とAI・5Gが牽引する技術的背景

半導体の歴史は、シリコンウェハー上に形成されるトランジスタをいかに縮小するかという「前工程(Front-end process)」の進化と同義でした。しかし現在、最先端のロジック半導体は3nmから2nm、さらにはオングストローム世代へと突入し、回路線幅は原子レベルの物理限界に到達しつつあります。EUV(極端紫外線)露光装置への数百億円規模の巨額投資や、ショートチャネル効果を抑制するためのGAA(Gate-All-Around)構造などの複雑なプロセス開発により、トランジスタあたりの製造コストはかつてないペースで高騰しています。さらに、生成AI向けに巨大な単一シリコンダイ(モノリシックダイ)を製造しようとすれば、微小な欠陥による歩留まり低下が致命的となり、経済的な破綻を招きかねません。

一方で、大規模言語モデル(LLM)の学習や5G/6Gによる大容量通信の進展は、プロセッサの演算能力以上に「メモリ帯域幅」に対して前例のない要求を突きつけています。演算ユニットとメモリ間のデータ転送速度がシステム全体の性能を律速する「フォン・ノイマン・ボトルネック」です。この「コストの壁」と「性能・帯域幅の壁」のギャップを同時に突破するアプローチとして浮上したのが、巨大なチップを機能ごとに分割して製造し、後工程で高密度に結合する「チップレット」アーキテクチャと、それらを立体的に統合する「3Dスタッキング」なのです。

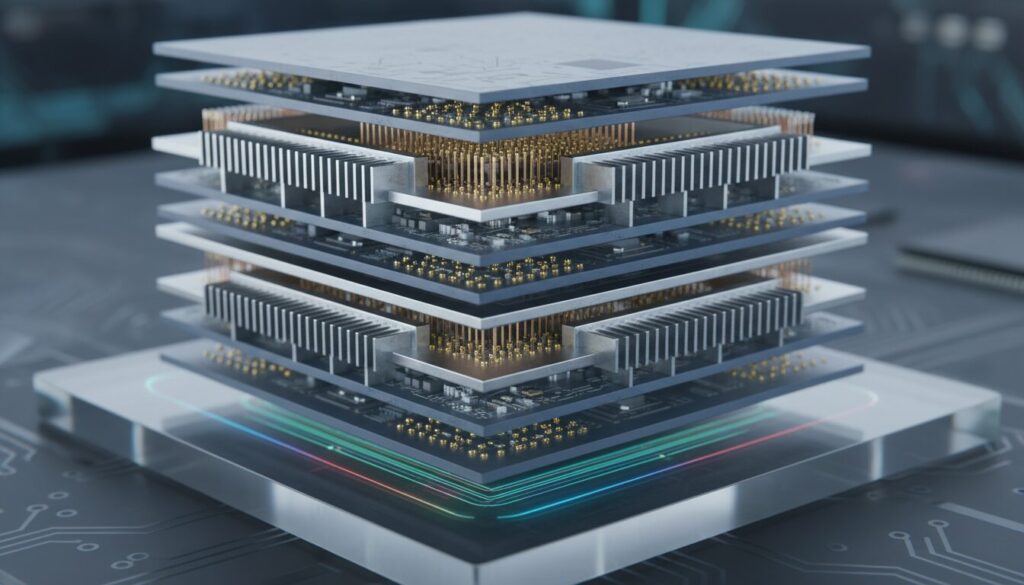

図解でわかる「2.5D実装」と「3D実装」の構造的な違い

アドバンスド・パッケージングの進化を正確に理解するためには、「2.5D実装」と「3D実装」の構造的および電気的なアプローチの違いを切り分ける必要があります。

2.5D実装は、シリコンインターポーザ(微細配線が施された中継基板)と呼ばれる土台の上に、ロジックICやHBM(広帯域メモリ)などの複数のチップレットを「平面的」に高密度配置する技術です。チップ間の通信はインターポーザ内の再配線層(RDL)を介して行われます。平面的な拡張であるため放熱設計が比較的容易であり、現在のハイエンドAIアクセラレータ(NVIDIAのH100等)でデファクトスタンダードとなっています。

対して、3D実装(3Dスタッキング)は、シリコンダイ同士を「垂直的(立体的)」に直接積み上げる究極の実装形態です。ダイ間の通信距離を数マイクロメートルレベルまで極限短縮することで、2.5D実装をはるかに凌駕する超広帯域通信、低遅延、および配線抵抗の低下による劇的な消費電力削減を実現します。

| 比較項目 | 2.5D実装 | 3D実装(3Dスタッキング) |

|---|---|---|

| 構造の基本概念 | インターポーザ上に複数のチップを平面的に並置 | チップまたはウェハーを垂直方向(Z軸)に直接積層 |

| チップ間通信の経路 | インターポーザ内の微細配線(RDL)を経由 | TSV (Through Silicon Via) による垂直方向の最短直結 |

| 主な接合方式 | マイクロバンプによるC4接続など | マイクロバンプ、またはハイブリッドボンディング |

| 通信遅延・電力効率 | 良好(既存の有機基板よりは圧倒的に優れる) | 究極的(オンチップ通信と同等の寄生容量・抵抗) |

| 代表的な適用事例 | AI学習用ハイエンドGPU、高性能ネットワークスイッチ | HBMの内部積層、積層型CMOSイメージセンサ、SRAM・ロジックの3D化 |

エコシステムの変革と「チップレット」標準化の波(UCIe等の動向)

3Dスタッキング技術が切り拓く最大の可能性は、ヘテロジニアス・インテグレーション(異種デバイスの統合)です。最先端プロセス(例:3nm)で作られた高性能演算コアと、成熟プロセス(例:12nm)で作られたアナログ回路やI/Oインターフェースを混載することで、システム全体の開発コストを劇的に引き下げることができます。

しかし、この構想を業界全体で実現するためには、異なるファウンドリで製造されたチップレット同士がシームレスに通信するための「共通言語」が不可欠です。そこで現在、Intel、TSMC、Samsungをはじめとする業界のトッププレイヤーが主導し、UCIe (Universal Chiplet Interconnect Express)と呼ばれるダイ間通信のオープンな標準規格の策定が急ピッチで進められています。PCIeやCXLなどの既存プロトコルを包含し、パッケージレベルでのインターフェースを標準化することで、企業はレゴブロックを組み立てるように他社製のチップレットを調達し、3D実装を用いて独自のカスタムSoCを短期間で構築できるようになります。後工程はもはや単なる「パッケージング」ではなく、システムアーキテクチャそのものを再定義する設計の最前線となっているのです。

2. 3Dスタッキングを支えるコア接続技術:TSVから最新トレンドまで

TSV(シリコン貫通電極)とマイクロバンプの基礎と物理的限界

これまでの3次元実装の基礎を築き上げた基幹技術が、TSV (Through Silicon Via)とマイクロバンプの組み合わせです。TSVは、シリコンダイを貫通する微細な孔をDRIE(深堀り反応性イオンエッチング)技術で形成し、そこに銅などの導電性材料を電解めっきで充填することで、ダイの表裏を最短距離で結ぶ垂直配線技術です。従来のワイヤーボンディングが基板の外周を引き回す必要があったのに対し、TSVはI/O密度を桁違いに向上させました。

しかし、純粋な3Dスタッキングとしてダイ同士を垂直に直接接続する際、はんだをベースとしたマイクロバンプは物理的な微細化限界に直面しています。バンプのピッチ(間隔)を40μm以下に縮小しようとすると、熱圧着時にはんだが横に押し潰されて隣の電極と接触する「ブリッジング(ショート)」が発生しやすくなります。また、高電流密度下では金属原子が移動してしまう「エレクトロマイグレーション」による断線リスクも跳ね上がります。AIプロセッサが要求する「テラバイト級の帯域幅」を満たすためには、物理的な金属の「球」に依存しない、次なるブレイクスルーが不可欠でした。

次世代の主役「ハイブリッドボンディング」とWOW/COW積層の深掘り

マイクロバンプの限界を打ち破る次世代パッケージングの主役として、爆発的な投資を呼び込んでいるのがハイブリッドボンディング(Cu-Cu直接接合)です。これは、ウェハ表面の銅電極と周囲の絶縁膜(SiO2やSiCNなど)を、CMP(化学機械研磨)を用いてナノメートル単位で極限まで平坦化し、プラズマ照射による表面活性化を経て、室温でまず絶縁膜同士を親水性結合させます。その後、200〜300℃程度のアニール(熱処理)を行うことで、銅の熱膨張を利用して電極同士を物理的に押し付け合い、強固な金属結合を一括で形成する無バンプ技術です。電極ピッチを数μmからサブミクロン領域にまで縮小可能とし、I/O密度を従来比で1,000倍以上に引き上げます。

実装手法としては、以下の2つのアプローチが覇権を争っています。

- WOW (Wafer-on-Wafer): ウェハ同士を直接貼り合わせる手法。アライメント精度が高く、製造スループットが極めて高いため、フラッシュメモリの3D化や積層型イメージセンサなど、同種ダイの高密度積層に最適です。

- COW (Chip-on-Wafer): 切り出された個別のダイを、ベースウェハ上の特定位置に高精度にマウントして積層する手法。プロセスの異なる異種チップレットを柔軟に統合でき、良品ダイのみを選別して積層できるため、ハイエンドロジックの統合において現在主流となっています。

最新研究:TSVやバンプの限界を超える「バンプレス積層技術」

ハイブリッドボンディングのさらに先を見据えた最先端研究も進行しています。東京工業大学(現・東京科学大学)などが提唱するバンプレス積層(BBCU:Bumpless Build-up Cu技術など)は、TSVの概念すらも過去のものにするポテンシャルを秘めています。

TSVはシリコンを貫通するため、その分だけトランジスタを配置できる貴重なシリコン面積(Keep-Out Zone)を犠牲にします。BBCU技術では、極薄の接着性樹脂でウェハを接合した後、フォトリソグラフィと電解めっきを用いて、ダイ間を直接太く短い銅配線で結びます。シリコン基板を極限まで薄化し、貫通電極を用いることなく配線層同士を直接コンタクトさせることで、寄生容量とインダクタンスを劇的に低減させ、RC遅延を理論上の限界値にまで近づけることが可能です。これにより、チップ間通信の消費電力はオンチップ(同一ダイ内)での通信とほぼ同等になります。

技術的な落とし穴:ナノレベルの歩留まり管理とテストの壁

理論上は完璧に見える3Dスタッキングですが、量産現場には深刻な「落とし穴」が存在します。その最たるものが、パーティクル(微粒子)管理とテスト(検査)の壁です。

ハイブリッドボンディングは分子間力を用いた接合であるため、接合面にわずか数ナノメートルのパーティクルが一つ介在するだけで、その周囲数十マイクロメートルにわたって接合不良(ボイド)が発生します。WOWプロセスの場合、この一つのゴミが原因で高価な最先端ウェハ全体が不良品となるリスクを孕んでいます。

また、積層前後のテスト技術も大きな課題です。3D積層を行う前に、ダイが完全に正常であることを保証する「KGD(Known Good Die:良品ダイ)」の確保が必須ですが、ウェハ状態でのフルスピードテストは技術的に極めて困難です。さらに、積層後には下層のダイに物理的にプローブ針を当てることができなくなります。そのため、チップ内部に自己診断回路を組み込むBIST(Built-In Self Test)や、一部のTSVが断線していても予備の経路に切り替える冗長回路設計(Redundancy)など、ハードウェア設計段階からのDft(Design for Testability)アプローチが不可欠となっています。

3. 実装における2大課題(放熱・コスト)と材料技術による解決アプローチ

3Dスタッキング最大の障壁「ダークシリコン問題」と熱応力(反り)

2.5D実装から3Dスタッキングへの移行において、物理学的に最も深刻なボトルネックとなるのが「熱」です。複数のロジックダイやメモリダイを垂直に積み上げることで、チップ単位面積あたりの消費電力(熱密度)は桁違いに上昇します。特に、下層のロジックチップから発生する強烈な熱が上層チップに直撃し、熱暴走やリーク電流の増大を引き起こす現象は、稼働できない回路領域を生む「ダークシリコン問題」として開発者を悩ませています。

同時に、製造プロセスにおいて致命的となるのが熱応力(Warpage:反り)です。シリコンダイ、銅のTSV、そして有機基板はそれぞれ異なる熱膨張係数(CTE:Coefficient of Thermal Expansion)を持っています。リフロー炉などで高温の熱処理を加えた後、室温に戻る過程で材料間の収縮率の違いからパッケージ全体が弓なりに反り返り、内部のマイクロバンプが引き剥がされたり、TSVにクラック(亀裂)が入ったりする現象が頻発します。ダイ間の距離が数マイクロメートルレベルに近接する3D実装では、このナノレベルの応力制御が歩留まりを左右する決定的な要因となります。

製造コストの膨張とKGD(良品ダイ)確保のジレンマ

3Dスタッキングは、本来「歩留まりの悪い巨大ダイを分割してコストを下げる」ための技術ですが、皮肉なことに積層工程そのものが新たな巨大コストリスクを生み出しています。数式で表せば、最終的なパッケージの歩留まり(Y_total)は、積層される各ダイの歩留まり(Y_die)と接合工程の歩留まり(Y_bonding)の掛け算となります。

例えば、99%の良品率を誇るKGDを4枚積層し、各接合工程の歩留まりが95%だった場合、最終歩留まりは約81%まで低下します。もし接合工程で失敗すれば、下層に積み上げた高価なHBMや最先端ロジックダイを含め、パッケージ全体を丸ごと廃棄(キル)しなければなりません。この「複合的な歩留まり低下リスク」こそが、3D実装の製造コストを跳ね上げている最大の要因であり、ファウンドリ各社が接合装置の精度向上に血眼になっている理由です。

課題を克服する「材料選定」:封止材、NCF、次世代TIMの重要性

これらのハードウェア的・熱力学的な限界を打破するためには、装置だけでなく「材料化学の力」が不可欠です。ダイ間の微小な空間を制御し、熱を逃がし、応力を吸収する特殊なポリマー材料が後工程の成否を握ります。

- アンダーフィルとNCF(非導電性フィルム): マイクロバンプの隙間に毛細管現象で液体樹脂を流し込む従来のCUF(Capillary Underfill)は、ピッチ微細化により充填時に気泡(ボイド)が残りやすくなりました。これに代わり、あらかじめウェハにラミネートしておき、熱圧着と同時に瞬時に溶融・硬化(スナップキュア)してボイドレス接合を実現するNCFの採用が進んでいます。

- 応力制御(低CTE化): シリコンと基板の熱膨張差による反りを防ぐため、アンダーフィルやモールド樹脂には、ナノレベルのシリカフィラーを高密度かつ均一に分散させ、樹脂全体のCTEをシリコンに極限まで近づける超絶技巧が求められます。

- 次世代TIM(Thermal Interface Material): 垂直にこもる熱を外部のヒートシンクへ逃がすため、熱伝導率を極限まで高めた放熱材料(TIM)の開発が急務です。高熱伝導フィラーを高充填したポリマーだけでなく、近年では液体金属(Liquid Metal)やグラフェン、カーボンナノチューブを応用した次世代TIMの社会実装テストが進められています。

4. チップレット時代の3D実装市場予測と日本の競争優位性

2026〜2030年の技術予測シナリオ:光電融合とガラス基板の台頭

市場調査機関の予測によれば、先進パッケージング市場は2030年までに数百億ドル規模へと倍増し、3D実装分野は年平均成長率(CAGR)30%超という爆発的な成長が見込まれています。2026年以降の技術トレンドとして、現在横並びで配置されているGPUとHBMの関係は、HBM4およびHBM5世代において、ロジックダイの直上にメモリを直接ハイブリッドボンディングで積層する真の「3D-SoC」へと進化する見通しです。

さらに、大面積化するパッケージを支える土台として、従来の有機基板から、平坦性に優れ微細配線が可能な「ガラス基板(Glass Core Substrate)」へのパラダイムシフトが2020年代後半に本格化します。また、増大し続けるデータ転送の消費電力を劇的に削減するため、電気信号を光信号に変換する光トランシーバをチップと同じパッケージ内に統合するCPO(Co-Packaged Optics:光電融合技術)の実用化も目前に迫っています。3Dスタッキングは、電子と光の境界線すらも内包する技術へと変貌を遂げようとしています。

後工程市場を牽引する国内メーカーの動向と「チョークポイント」の支配

この急成長する次世代後工程市場において、特筆すべきは日本企業の圧倒的な競争優位性です。前工程(微細化露光など)では一部の海外メガファウンドリにシェアを譲った日本ですが、3Dスタッキングを具現化するための「装置と材料」のエコシステムにおいては、世界のサプライチェーンの要衝(チョークポイント)を完全に支配しています。

ウェハをナノレベルで平滑化するCMP(化学機械研磨)装置、ダメージゼロでダイを切り出すプラズマダイシング装置、そして接合時のボイドを非破壊で高速検出する3D-X線検査装置など、最先端の実装ラインは日本の製造装置なしでは稼働しません。さらに材料領域でも、ビルドアップ基板用の絶縁フィルム、微細ピッチ対応の感光性絶縁材料、高機能NCFや放熱シート(TIM)に至るまで、日本国内の化学・素材メーカーが世界シェアの過半数を握っています。これら「すり合わせ技術」の結晶である高機能材料群は、競合他社が容易に模倣できない強固な技術的モート(堀)を形成しています。

経済安全保障とサプライチェーン再構築のインパクト:次世代覇権の行方

米中デカップリングや地政学リスクが高まる中、最先端のパッケージング能力の確保は、単なる企業間競争を超えた「国家の経済安全保障」の核心に位置付けられています。現在、TSMCやIntel、Samsungといった前工程の巨人が独自の3D実装技術(CoWoS/SoIC、Foveros等)を内製化し、従来のOSAT(後工程受託製造企業)の領域を侵食する「Foundry 2.0」と呼ばれる業界構造の融合が起きています。

各国政府が巨額の補助金を投じて自国内への先進パッケージング拠点の誘致を進める中、日本は装置・材料のハブとしての地位を最大限に活用し、世界のメガファウンドリの研究開発拠点を相次いで国内に引き寄せています。チップレット時代の勝敗は、「いかに微細なトランジスタを作るか」だけでなく、「いかに高度な材料と装置のエコシステムを巻き込み、立体的な熱と電気の壁を克服するか」に懸かっています。次世代のコンピューティング覇権は、まさにこの3Dスタッキングという「深淵なる後工程」を制する者が握ることになるのです。

よくある質問(FAQ)

Q. 3Dスタッキングとは何ですか?

A. 3Dスタッキング(3次元積層)とは、複数の半導体チップを立体的に積み重ねて統合する最先端の実装技術です。従来のトランジスタ微細化が物理的・コスト的な限界を迎える中、それに代わって性能向上を図る手法として注目されています。生成AIの爆発的普及やデータセンターの高度化を根底から支える重要な技術です。

Q. 2.5D実装と3D実装の違いは何ですか?

A. 2.5D実装は、基板(インターポーザ)上に複数のチップを平面的に並べて高密度に接続する手法です。一方、3D実装はチップ自体を直接立体的に積み重ねるため、実装面積をさらに削減し、配線距離を極限まで短縮できます。微細化の限界を超えるため、用途に応じた使い分けやハイブリッド化が進んでいます。

Q. 3Dスタッキングの課題やデメリットは何ですか?

A. 最大の障壁は「放熱」と「製造コスト」です。立体的に積層するため内部に熱がこもりやすく、熱応力によるチップの反りや「ダークシリコン問題」が発生します。また、ナノレベルの歩留まり管理や、積層前にすべてのダイを良品(KGD)で揃える必要があり、製造およびテストコストの膨張が深刻な課題となっています。