現代のエレクトロニクス産業は、半導体の微細化が物理的な限界に達する「ムーアの法則の終焉」と、それに伴うリーク電流の増大、いわゆる「ダークシリコン問題」という極めて深刻な壁に直面しています。サイバー空間とフィジカル空間が高度に融合するSociety 5.0時代において、爆発的に増加するAIサーバーやIoTデバイスの消費電力をいかに抑えるかは、地球規模の課題です。この限界を根本から打破し、次世代コンピューティング・アーキテクチャの根幹を再定義する究極の基盤技術として、世界中のメガテック企業やビジョナリーな投資家から巨額の資金を集めているのが「スピントロニクス(Spintronics)」です。

本記事では、電子の持つ「電荷」と「スピン(磁気的性質)」の双方を制御するスピントロニクスの基礎原理から、最前線でのデバイス実装、次世代マテリアルのブレイクスルー、実用化における技術的落とし穴、そして2026〜2030年を見据えた産業・投資シナリオに至るまで、圧倒的な深度で包括的に解説します。

- スピントロニクスとは?従来のエレクトロニクスとの決定的な違い

- 電子の「電荷」と「スピン」を同時利用するパラダイムシフト

- ノーベル物理学賞(GMR効果)から始まる歴史的背景と技術的系譜

- スピントロニクスを支える基本原理と中核技術

- 情報を記憶するコア構造:磁気トンネル接合(MTJ)の仕組み

- 高効率な書き込みを実現する「スピン注入トルク(STT)」と次世代技術への昇華

- なぜ今注目されるのか?スピントロニクスがもたらす3大メリットと競合比較

- 待機電力ゼロへ:非揮発性が実現する「究極の省電力」とノーマリーオフ

- 既存技術及び他の次世代メモリ(ReRAM/PCRAM等)との徹底比較

- デバイス応用と最新研究の最前線:MRAMから新材料までの技術的課題

- 次世代不揮発性メモリ「MRAM」の実装状況と製造上のボトルネック

- 超低消費電力を極める新材料「トポロジカル絶縁体」の物理的優位性

- AI・IoT時代を牽引する次世代コンピューティングへの応用

- エッジAIを根底から支えるインメモリ・コンピューティングの衝撃

- 人間の脳を模倣する「脳型(ニューロモルフィック)コンピューティング」

- 【CTO・投資家向け】産業インパクトと2026〜2030年のビジネス・投資シナリオ

- 実用化のロードマップ:第4世代までの技術進化と市場予測シナリオ

- テック系投資家・経営層が注視すべきエコシステムとバリューチェーン

スピントロニクスとは?従来のエレクトロニクスとの決定的な違い

スピントロニクス(Spintronics:Spin Transport Electronicsの略称)とは、電子が持つ「電荷(電気的な性質)」と「スピン(磁気的な性質:自転に例えられる角運動量)」の双方を同時に工学的に制御・利用する次世代の基盤技術です。従来の半導体技術であるエレクトロニクスが電荷の移動(電流)のみに依存して情報の処理と伝送を行っていたのに対し、スピンという新たな自由度を組み込むことで、情報処理と情報記憶のあり方を根本から覆すパラダイムシフトを引き起こしています。

電子の「電荷」と「スピン」を同時利用するパラダイムシフト

従来のエレクトロニクスは、トランジスタを微細化することで処理能力を高め、コストを下げる「ムーアの法則」に従って性能向上を遂げてきました。しかし現在、プロセスルールが数ナノメートル単位にまで到達した結果、量子トンネル効果による「リーク電流(漏れ電流)」が激増し、チップが発熱して性能が頭打ちになる「ダークシリコン問題」に直面しています。この致命的な物理的限界を打破するアプローチがスピントロニクスです。

電子のスピンには「上向き(Up)」と「下向き(Down)」という2つの状態が存在します。このスピンの向きを磁性体内部で揃え、巨視的な「磁化の方向」として情報の「0」と「1」に対応させることで、電源を切っても情報が消滅しない非揮発性(Non-volatility)の獲得が可能となります。電荷ベースのデバイスでは、状態を維持するために常に電力を供給(リフレッシュ等)し続けなければなりませんが、スピンベースのデバイスは、物理的な磁化として状態が固定されるため、待機電力を一切必要としません。

ノーベル物理学賞(GMR効果)から始まる歴史的背景と技術的系譜

スピントロニクスがこれほどの産業的・投資的インパクトを持つに至った歴史の起点は、1988年にフランスのアルベール・フェール氏とドイツのペーター・グリュンベルク氏によって独立に発見されたGMR効果(巨大磁気抵抗効果:Giant Magnetoresistance)に遡ります。数ナノメートルという極薄の強磁性層と非磁性金属層を交互に重ねた積層構造において、外部の磁場によって電気抵抗が数十パーセントも劇的に変化するこの現象は、物理学界に衝撃を与えました。

この基礎研究はまたたく間に産業化され、1990年代後半にはハードディスクドライブ(HDD)の読み取りヘッド(リードヘッド)に実装されました。GMRヘッドの導入により、HDDのデータ記録密度は数万倍へと爆発的に引き上げられ、現在のクラウド・データセンターを支える大容量ストレージの基盤が確立しました。この圧倒的な功績により、両氏は2007年にノーベル物理学賞を受賞しています。

GMR効果の成功は、エレクトロニクス産業における「第一世代のスピントロニクス」に過ぎません。その後の研究は、絶縁体を挟み込んだ構造におけるトンネル磁気抵抗(TMR)効果の室温動作の実現を経て、次世代の不揮発性メモリであるMRAM(磁気ランダムアクセスメモリ)へと技術的系譜を受け継ぎ、現在は「記憶装置」から「演算装置」の領域へとその応用範囲を爆発的に広げています。

スピントロニクスを支える基本原理と中核技術

現在のスピントロニクスデバイス、とりわけ高度なコンピューティングアーキテクチャを支えるコア技術は、ナノスケールの材料科学と量子力学の結晶です。本セクションでは、次世代デバイスの実装においてCTOや先端研究者が最も注視する「情報の記憶」と「情報の書き換え」を担う二大要素技術について、物理的なメカニズムと最新の知見を深く掘り下げます。

情報を記憶するコア構造:磁気トンネル接合(MTJ)の仕組み

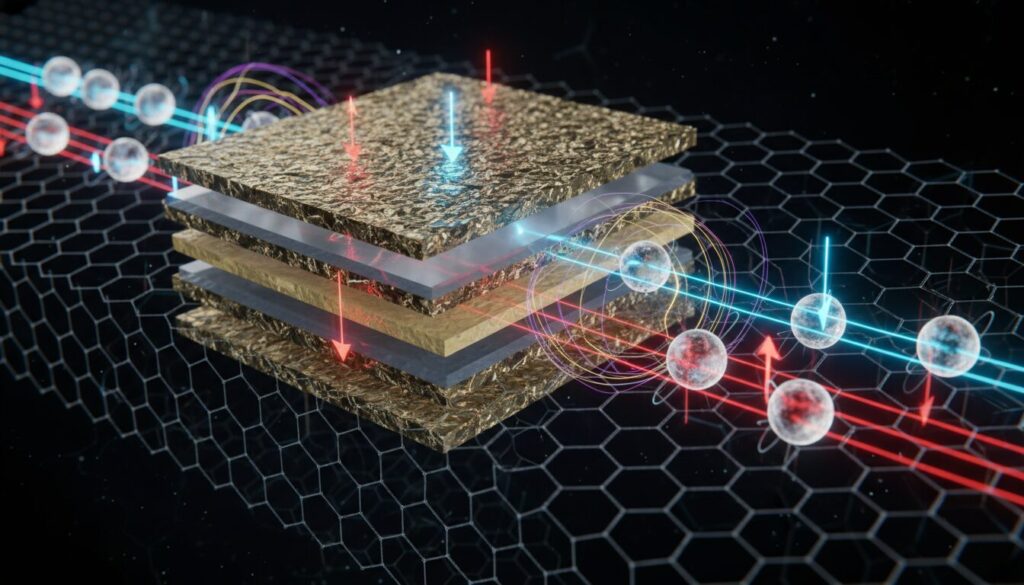

スピントロニクスデバイスにおいて、情報を記憶し、それを電気信号として読み出す心臓部となるのが磁気トンネル接合(MTJ:Magnetic Tunnel Junction)素子です。MTJはナノスケールの薄膜積層構造を持ち、主に以下の3層から構成されています。

- 固定層(ピン層/Reference Layer):スピンの向き(磁化の方向)が常に一方向に強固に固定された強磁性層。

- トンネルバリア層:厚さ1〜2ナノメートル程度の極薄の絶縁体。現在は、格子整合性に優れ、巨大な抵抗変化を生み出す酸化マグネシウム(MgO)の単結晶薄膜が絶対的なデファクトスタンダードとなっています。

- 自由層(フリー層/Free Layer):外部からの物理的刺激(スピン流など)によって、スピンの向きを反転させることができる強磁性層。この層の磁化の向きがデータを保持します。

MTJの画期的な点は、固定層と自由層の「磁化方向の相対関係」によって、素子全体の電気抵抗が劇的に変化するトンネル磁気抵抗(TMR)効果を利用していることです。両層の磁化が同じ向き(平行状態)のときは、スピン分極した電子がトンネルバリアを量子力学的に通過しやすく、「低抵抗状態(データ”0″)」となります。逆に、磁化が反対向き(反平行状態)のときは、電子の通過が阻害されて「高抵抗状態(データ”1″)」となります。

最前線の実装現場では、微細化に伴う熱揺らぎによるデータ消失を防ぐため、磁化を薄膜の水平方向ではなく垂直方向に向ける垂直磁化MTJ(p-MTJ:Perpendicular MTJ)が採用されています。界面の強力な垂直磁気異方性(PMA)を利用することで、数ナノメートルの極小サイズでも10年以上のデータ保持特性(熱安定性)を確保することが可能となっています。

高効率な書き込みを実現する「スピン注入トルク(STT)」と次世代技術への昇華

MTJにおいて読み出し技術(TMR効果)が確立された後、2000年代にかけて業界最大のボトルネックとなっていたのが「いかにして効率よく、かつ省電力で自由層の磁化(情報)を書き換えるか」という課題でした。初期のMRAMは外部配線に電流を流して磁場を発生させる手法(トグル方式)を用いていましたが、微細化するほど隣接セルへの誤書き込み(クロストーク)が発生し、消費電力も増大するという致命的な欠陥がありました。これを解決し、スピントロニクスに真のパラダイムシフトを引き起こしたのがスピン注入トルク(STT:Spin Transfer Torque)技術です。

STTは、外部磁場を一切使用せず、スピンの向きが揃った電子の波(スピン偏極電流)をMTJ素子に直接流し込むことで磁化を反転させる量子力学的技術です。固定層を通過してスピンの向きが「整列」した電子群が自由層に流れ込む際、電子自身が持つ「スピン角運動量」が自由層の局在スピンに受け渡され、物理的なトルク(回転力)として作用します。このトルクが一定のしきい値(臨界反転電流)を超えると、自由層の磁化がパタッと反転し、データが書き換えられます。

STTの最大の物理的優位性は、「素子を微細化するほど、書き換えに必要な電流値が低下する」という優れたスケーリング則をもたらした点にあります。これにより、先端ロジック半導体のプロセスノードに適合する超高集積化が可能となりました。

さらに現在、R&Dの最前線ではSTTの限界(書き込み速度の壁と、トンネル絶縁膜への電気的ストレス)を突破するため、スピン軌道トルク(SOT:Spin Orbit Torque)技術の開発が急加速しています。SOTは、重金属やトポロジカル絶縁体に電流を流した際に生じるスピンホール効果を利用して「純スピン流」を生成し、隣接する磁性層に強烈なトルクを与える技術です。読み出し経路と書き込み経路を物理的に分離(3端子構造)できるため、絶縁膜の破壊リスクをゼロにしつつ、ピコ秒〜サブナノ秒オーダーというSRAMを凌駕する超高速書き込みを実現します。

なぜ今注目されるのか?スピントロニクスがもたらす3大メリットと競合比較

現在、サイバー空間を支える巨大なデータセンターから、末端のIoTエッジデバイスに至るまで、システム全体の電力消費の多くを「メモリのデータ保持」と「メモリ・プロセッサ間のデータ移動」が占めています。スピントロニクスが世界中のCTOや投資家から熱狂的に支持される理由は、単なるスペックの向上ではなく、現在のフォン・ノイマン型アーキテクチャが抱える制約を破壊する「超低消費電力」「超高速動作」「半永久的な高耐久性」という3つの優位性を同時に実現できるからです。

待機電力ゼロへ:非揮発性が実現する「究極の省電力」とノーマリーオフ

現在主流であるCPUのキャッシュメモリ(SRAM)やメインメモリ(DRAM)は揮発性メモリであり、データを保持するために常に電力を供給し続けるか、定期的なリフレッシュ動作を行う必要があります。スピントロニクス応用デバイスの筆頭であるSTT-MRAMは、スピンの物理的な向きとしてデータを記録するため、完全な非揮発性を持ちます。これにより、電源を完全に遮断してもデータは失われず、システムの待機電力を実質ゼロに抑え込むことが可能です。

この特性をシステムレベルで活用したのがノーマリーオフ・コンピューティング(Normally-off Computing)です。演算が必要なミリ秒単位の瞬間だけシステムに電源を入れ、処理が終われば即座に電源を完全に落とす。データはオンチップのMRAMに保持されているため、復帰のための遅延(ブートアップ時間)やデータの再ロードは発生しません。このアーキテクチャにより、スマートウォッチや産業用センサー、体内埋め込み型医療デバイスなどのバッテリー駆動時間を数倍から数十倍に延長し、環境発電(エナジーハーベスト)のみで永続稼働する究極のエッジデバイスの構築が可能となります。

既存技術及び他の次世代メモリ(ReRAM/PCRAM等)との徹底比較

非揮発性メモリ領域には、NANDフラッシュの他にも、抵抗変化型メモリ(ReRAM)、相変化メモリ(PCRAM)、強誘電体メモリ(FeRAM)など、多くの競合技術が存在します。しかし、CPUのキャッシュメモリや高度なエッジAIのワーキングメモリとして要求される「ナノ秒オーダーの速度」と「無限に近い耐久性」を両立できるのは、現時点でスピントロニクス(STT-MRAMおよびSOT-MRAM)のみです。

以下の表は、各メモリ技術の特性とトレードオフを網羅的に比較したものです。CTOやシステムアーキテクトにとって、スピントロニクスがいかに特異で強力なポジションを占めているかが一目で理解できるはずです。

| メモリの種類 | 揮発性 | 書き込み速度 | 書き換え耐久性 | 技術的課題・落とし穴 | 主な用途・実装領域 |

|---|---|---|---|---|---|

| SRAM | 揮発性 | 超高速(<1ns) | 実質無限 | セル面積が大きく(6トランジスタ)、待機電力(リーク電流)が膨大 | CPUのL1/L2キャッシュ |

| DRAM | 揮発性 | 高速(〜10ns) | 実質無限 | リフレッシュ動作が必須。微細化に伴うキャパシタ形成の物理的限界 | メインメモリ(RAM) |

| NAND Flash | 非揮発性 | 低速(100µs〜1ms) | 有限(10^3〜10^5回) | 高電圧駆動が必要。絶縁膜の劣化による寿命制限がシビア | 大容量ストレージ(SSD等) |

| ReRAM / PCRAM | 非揮発性 | 中速(10ns〜100ns) | 有限(10^6〜10^9回) | フィラメント形成や相変化時の熱ストレスによる素子劣化。ばらつき制御 | ストレージクラスメモリ、アナログAI重み保持 |

| STT-MRAM (スピントロニクス) |

完全非揮発 | 高速(2ns〜10ns) | ほぼ無限(10^12〜10^15回) | SRAM対比でのセル面積縮小と、書き込み時のトンネルバリア負荷 | L3キャッシュ代替、車載MCU、エッジAI |

NANDやReRAM、PCRAMがいずれも原子・分子レベルの物理的な移動や相変化(溶融・結晶化など)を伴うのに対し、MRAMは「電子のスピン(磁化方向)の反転」という純粋な量子力学的現象のみを利用します。そのため、物理的な構造の摩耗が一切発生せず、事実上無限の耐久性を誇るのです。この特性が、頻繁にデータの書き換えが発生するAI推論やロジック混載領域における絶対的な優位性を担保しています。

デバイス応用と最新研究の最前線:MRAMから新材料までの技術的課題

基礎物理の発見から数十年を経て、スピントロニクスは今まさに「量産化」と「破壊的イノベーションの準備」という二つのフェーズを同時に迎えています。本セクションでは、量産化が本格化しているMRAMの最前線の製造課題と、未来のコンピューティングを刷新する新材料の可能性を解き明かします。

次世代不揮発性メモリ「MRAM」の実装状況と製造上のボトルネック

現在、TSMC、Samsung、Intel、GlobalFoundriesなどのメガファウンドリは、22nmや16/14nmのFinFETプロセスにおいて、既存の組み込みフラッシュメモリ(eFlash)を代替するソリューションとしてeMRAM(組み込み型MRAM)の量産を本格化させています。特に、高熱環境下での高い信頼性が求められる自動車産業(車載マイコン)や、バッテリー寿命が絶対条件となるIoTデバイス市場において、急速にシェアを拡大しています。

しかし、MRAMがSRAMやDRAMを完全に駆逐し、すべてのメモリ階層を統合する「ユニバーサルメモリ」として普及するためには、製造プロセスにおけるシビアな技術的落とし穴(ボトルネック)を克服する必要があります。

- 微細加工における「レッドポ(再付着)」問題: MTJ素子は、コバルト鉄ボロン(CoFeB)やルテニウム(Ru)、酸化マグネシウム(MgO)など、多種多様な金属と絶縁体の積層膜から構成されます。これらを数ナノメートル単位で垂直にエッチングする際、削られた金属が素子の側壁に再付着(レッドポジション)し、ショートを引き起こす問題が深刻です。これを防ぐための高度なイオンビームエッチング技術や反応性イオンエッチング(RIE)の最適化が、歩留まり向上の鍵を握っています。

- 熱安定性と書き込み電流のトレードオフ: 素子を微細化するほど、熱揺らぎに対して磁化を保持する力(熱安定性)が低下します。これを補うために垂直磁気異方性(PMA)を強めると、今度は磁化を反転させるために必要な書き込み電流が増大してしまうというジレンマが存在します。

超低消費電力を極める新材料「トポロジカル絶縁体」の物理的優位性

前述のトレードオフを根本から解決し、MRAMのさらなる超高速化と低電力化を実現する次世代技術として、世界中の物理学者と材料工学者が熱狂しているのがトポロジカル絶縁体(Topological Insulator)という革新的な量子マテリアルです。

トポロジカル絶縁体(ビスマス・アンチモン合金など)とは、物質の内部は電流を全く通さない絶縁体でありながら、表面やエッジ(端)部分にのみ質量を持たない「ディラック電子」が存在し、金属的な伝導状態を示す特殊な物質です。この表面状態では、電子の運動方向とスピンの向きが直交して完全に固定される「スピン運動量ロッキング(Spin-Momentum Locking)」という特異な量子現象が発現します。

この性質を次世代のSOT-MRAMに応用することで、従来では考えられないほど高効率な「純スピン流」を生成できます。従来のSOTデバイスでは白金(Pt)やタングステン(W)といった重金属が用いられてきましたが、トポロジカル絶縁体を用いることで、スピンホール角(電流からスピン流への変換効率を示す指標)が重金属の数十倍から数百倍に達することが実証されています。これにより、磁化反転に必要な書き込み電流を一桁以上削減することが可能となり、発熱を極限まで抑えた超高密度のメモリ集積化への道が拓かれました。実用化に向けた最大の課題は、このトポロジカル表面状態を室温環境下で安定的に維持し、シリコンウェハー上に均一に成膜する量産技術の確立にシフトしています。

AI・IoT時代を牽引する次世代コンピューティングへの応用

スピントロニクスは、もはや単なる「データを保存するストレージやメモリ」の代替技術にとどまりません。高速な状態変化と非揮発性、そしてアナログ的な抵抗変化を組み合わせることで、コンピューティング・アーキテクチャそのものを根底から変革するポテンシャルを秘めています。特に、生成AIの台頭によって消費電力が爆発的に増加している現在、その解決策としてスピントロニクスを用いたハードウェア革新が注目されています。

エッジAIを根底から支えるインメモリ・コンピューティングの衝撃

現代のコンピュータの基礎である「フォン・ノイマン型アーキテクチャ」は、演算を行うCPUやGPUと、データを記憶するメモリ(DRAM等)が物理的に分離しています。ディープラーニングのような膨大な行列演算(積和演算:MAC演算)を行う際、プロセッサとメモリの間で絶え間なくデータの移動が発生します。実は、AI処理における消費電力と処理遅延の大部分は、演算そのものではなく、この「データの移動」に費やされています(フォン・ノイマン・ボトルネック)。

スピントロニクスは、この問題を解決するインメモリ・コンピューティング(Compute-in-Memory:CiM)の最強のハードウェア基盤となります。MRAMのコアであるMTJ素子は、ロジック回路(CMOS)の直上に積層することが容易です。これにより、メモリセルの内部、あるいは極めて近傍で直接アナログ的な積和演算を実行することが可能になります。データを外部メモリに読み出しに行く必要がなくなり、データ転送によるエネルギー損失とレイテンシを数十分の一から数百分の一にまで削減できます。これにより、クラウドに依存せず、スマートフォンや産業用ロボットの端末側で大規模言語モデル(LLM)や高度な画像推論を実行する、真のエッジAIの社会実装が加速します。

人間の脳を模倣する「脳型(ニューロモルフィック)コンピューティング」

さらに一歩進んだ次世代のアーキテクチャとして、人間の脳の神経回路網をハードウェアレベルで直接再現する脳型コンピューティング(ニューロモルフィック・コンピューティング)へのスピントロニクス応用が、最先端の研究分野として急浮上しています。

スピントロニクスデバイスは、人間の脳の機能と驚くほど親和性が高い物理的特性を持っています。例えば、ナノスケールのMTJ素子への電流のかけ方によって、抵抗値を連続的(アナログ的)に変化させ、それを非揮発的に記憶させることができます。これは、人間の脳において学習によって結合強度が変化する「シナプス可塑性」の完全な物理的模倣です。

さらに近年注目を集めているのが、スピントロニクスの「弱点」を逆手に取ったアプローチです。極小のMTJ素子において、室温の熱エネルギーによってスピンの向きがランダムに反転してしまう「熱揺らぎ」の現象を利用し、0と1を確率的に出力する確率論的ビット(p-bit:Probabilistic bit)を構築する研究です。このp-bitをネットワーク化することで、量子コンピュータのように複雑な組み合わせ最適化問題や、生成AIにおけるサンプリング処理を、常温かつ極めて少ない消費電力で超高速に解く「確率論的コンピューティング(アニーリング・マシン)」の実現が期待されています。スピントロニクスは、エレクトロニクスと脳科学、そして統計物理学を融合させる究極のプラットフォームなのです。

【CTO・投資家向け】産業インパクトと2026〜2030年のビジネス・投資シナリオ

本稿の総括として、スピントロニクスがもたらすビジネス的価値と、今後のテクノロジー市場における覇権争いの行方を紐解きます。学術的な枠組みを離れ、企業のCTOがいかに自社の技術ロードマップに本領域を組み込むべきか、そしてテック系投資家がどのバリューチェーンに資本を投下すべきか、極めて実践的なインサイトを提供します。

実用化のロードマップ:第4世代までの技術進化と市場予測シナリオ

スピントロニクスの実用化は、ハードディスクの読み取りヘッドに応用されたGMR効果を「第1世代」とすれば、現在はMTJとSTTを活用した「STT-MRAM」が車載・IoT向けに量産化され始めた「第2世代」の成熟・普及期にあります。そして2026年以降、次なる10年を牽引する第3・第4世代の技術が市場に投入され、半導体エコシステム全体に数兆円規模の経済効果をもたらすと予測されています。

| フェーズ | 時期 | 中核技術・アーキテクチャ | 市場へのインパクトとビジネス予測シナリオ |

|---|---|---|---|

| 第2世代 (現在〜普及) |

〜2026年 | STT-MRAMの量産拡大 マイコンへのeMRAM混載 |

SRAMやeFlashの代替によるエッジデバイスの省電力化。CAGR(年平均成長率)30%以上で成長し、ウェアラブルや車載ADAS向けワーキングメモリのデファクト化。 |

| 第3世代 (発展期) |

2026〜2030年 | SOT-MRAMの実用化 トポロジカルマテリアルの導入 |

L2/L3キャッシュメモリの完全代替。データセンター向けプロセッサへの統合が進み、サーバーの待機電力と冷却コストを劇的に削減。インメモリ・コンピューティングの初期実装。 |

| 第4世代 (革新期) |

2030年以降 | スピンニューロモルフィック 確率論的コンピューティング |

CMOSとの完全ハイブリッド化による自律型AIハードウェア基盤の確立。生成AIの推論コストを現在の数万分の一に圧縮し、あらゆるエッジ端末に高度な知能を実装。 |

CTOが注視すべきは、メモリが単なる「記憶の保管庫」から「演算の主役」へと移行している点です。自社のシステムやプロダクトがエッジコンピューティングやリアルタイムAI処理に依存している場合、このアーキテクチャの転換(ノーマリーオフやインメモリコンピューティング)を前提としたソフトウェアスタックとOSの再設計に、今すぐ着手すべきです。

テック系投資家・経営層が注視すべきエコシステムとバリューチェーン

投資家や経営戦略部門にとって、スピントロニクス市場の真の旨味は、チップメーカーやメガファウンドリ単体ではなく、その周辺に広がる広範な「製造・設計エコシステム」のチョークポイント(ボトルネック)を押さえる企業に存在します。次なるユニコーン企業や株式市場の牽引役は、以下の3つのバリューチェーンから台頭するでしょう。

- 最先端の製造装置・検査装置(メトロロジー):

MTJの製造には、数原子層レベルの極薄膜をダメージなく数十層積層する特殊なスパッタリング装置と、前述の「レッドポ」を防ぐ超高精度なイオンビームエッチング装置が不可欠です。また、ウェハー上でスピンの配列状態やSTTの書き込み効率を非破壊・非接触でインライン検査するメトロロジー(計測・評価)装置市場は、量産フェーズにおいて爆発的な特需が見込まれます。 - 新規マテリアルの開発と高純度素材サプライヤー:

スピントロニクスデバイスの性能は、界面の質と材料特性に完全に依存します。トンネルバリアとなる高純度な酸化マグネシウム(MgO)のターゲット材や、次世代SOT向けにトポロジカル絶縁体、反強磁性体、ホイスラー合金などを精密合成し供給できる特殊素材・化学メーカーは、極めて高い参入障壁を築き、利益を独占するポテンシャルを持っています。 - 回路設計IP・EDAツールプロバイダー:

ファウンドリが提供するeMRAMプロセスを利用して、ファブレス企業が容易にチップを設計できるよう支援するエコシステムです。標準CMOS技術とのシームレスな統合を可能にするMRAM特化型のマクロIP(知的財産)コアや、スピンダイナミクスを正確にシミュレーションできる次世代EDAツールを提供する企業は、ライセンスビジネスの巨大な金脈を掘り当てることになります。

Society 5.0が掲げる「サイバー空間とフィジカル空間の高度な融合」を実現するためには、莫大なデータを極低遅延かつ超省電力で処理するエッジハードウェアが不可欠です。現在の電荷ベースの半導体技術の延長線上にその答えはなく、スピントロニクスこそがブレイクスルーの鍵を握っています。表面的な「次世代メモリ」という枠組みに囚われず、インメモリ・コンピューティングや脳型AIハードウェアへと連なる壮大なテクノロジー・パラダイムシフトを見据えることで、この破壊的イノベーションの最大の受益者となることができるはずです。

よくある質問(FAQ)

Q. スピントロニクスとは簡単に言うと何ですか?

A. スピントロニクスとは、電子が持つ「電荷」に加えて、磁気的性質である「スピン」の両方を制御・利用する次世代の基盤技術です。半導体の微細化限界(ムーアの法則の終焉)を根本から打破し、次世代コンピューティングの根幹を再定義する技術として世界中から巨額の投資を集めています。

Q. スピントロニクスと従来のエレクトロニクスの違いは何ですか?

A. 最大の違いは、電源を切っても情報が消えない「非揮発性」を持つ点です。従来のエレクトロニクスとは異なり、待機電力をゼロにする「ノーマリーオフ」を実現できるため、爆発的に増加するAIサーバーやIoTデバイスの消費電力を劇的に削減することが可能です。

Q. スピントロニクスの実用化はいつ頃ですか?

A. スピントロニクスを応用した次世代不揮発性メモリ「MRAM」の実装はすでに始まっており、2026年から2030年にかけて本格的な産業利用・投資が進むと予測されています。現在は製造上の課題解決や、さらなる省電力を実現する「トポロジカル絶縁体」などの新材料研究が進められています。